## Au5410 – 10 Output, LVCMOS, Ultra Low Jitter Buffer

### **General Description**

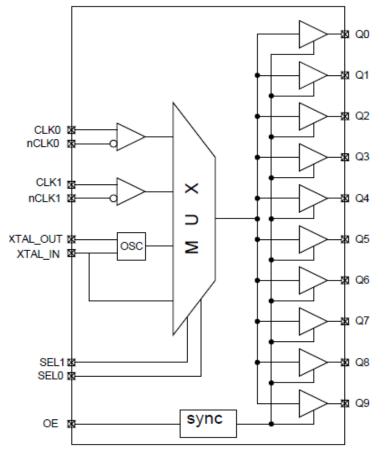

The Au5410 is a 10 output low-jitter clock, fan-out buffer, intended to be used in low jitter, high frequency clock/data distribution. The low impedance LVCMOS outputs are designed to drive 50  $\Omega$  series or parallel terminated transmission lines.

The buffer can choose a clock input from primary, secondary or crystal source. The primary and secondary clock sources can be single ended or fully differential. The selected clock is distributed to 10 LVCMOS output drivers.

The Au5410 operates from a 3.3 V/2.5 V/1.8 V core supply and 3.3 V/2.5 V/1.8 V/1.5 V output supply. The core supply and output supply are independent of each other and no supply sequencing is required.

#### **Features**

- Additive jitter performance of 50 fs RMS.

- Typical output skew between clock outputs is 30 ps

- Level translation with core supply voltage of 3.3 V/2.5 V/1.8 V and 3.3 V/2.5 V/1.8 V/1.5 V output supply for LVCMOS output drivers.

- The device inputs consists of primary, secondary and crystal inputs.

- The inputs are selected by programming input select pins of Au5410. The input clock receiver in Au5410 can accept LVPECL, LVDS, LVCMOS, SSTL, HCSL and XTAL waveforms.

- Crystal frequencies from 8 MHz to 50 MHz are supported.

- Crystal input can be over driven with frequency up to 250 MHz in crystal bypass mode

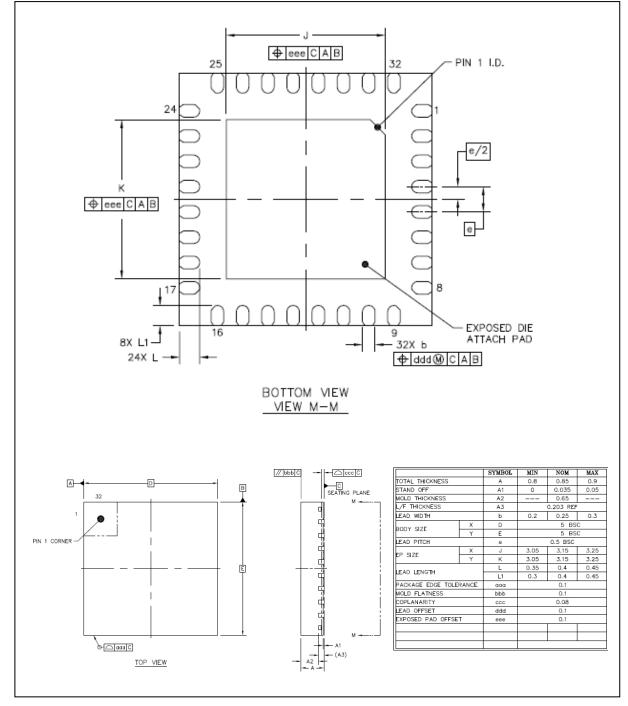

- Au5410 buffer is available in a 32-pin, 5mm X 5mm QFN package.

**Figure 1 Functional Overview**

## **Table of Contents**

| General Description                                                                                                                                | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Features                                                                                                                                           | 1  |

| Table of Contents                                                                                                                                  | 2  |

| List of Tables                                                                                                                                     | 3  |

| List of Figures                                                                                                                                    |    |

| 1 Detailed Pin Description                                                                                                                         |    |

| 2 Electrical Characteristics                                                                                                                       |    |

|                                                                                                                                                    |    |

| 3 Functional Description                                                                                                                           |    |

| 3.1 VDD and VDDO Power Supplies                                                                                                                    |    |

| 3.2 Clock Inputs                                                                                                                                   |    |

| <ul> <li>3.3 Clock States (Input vs Output States)</li> <li>3.4 Output Enable</li> </ul>                                                           |    |

|                                                                                                                                                    |    |

| 4 Application Information                                                                                                                          |    |

| 4.1 Driving the Clock Inputs                                                                                                                       |    |

| <ul> <li>4.1.1 Driving Clock Inputs with LVCMOS Driver (AC coupled)</li> <li>4.1.2 Driving Clock Inputs with LVCMOS Driver (DC coupled)</li> </ul> |    |

| <ul> <li>4.1.2 Driving Clock Inputs with LVCMOS Driver (DC coupled)</li> <li>4.1.3 Driving XTAL_IN with LVCMOS Driver (AC coupled)</li> </ul>      |    |

| 4.1.4 Driving XTAL_IN with LVCMOS Driver (AC coupled)                                                                                              |    |

| 4.1.5 LVDS (DC coupled)                                                                                                                            |    |

| 4.1.6 HCSL (DC coupled)                                                                                                                            |    |

| 4.1.7 LVPECL (DC coupled)                                                                                                                          |    |

| 4.1.8 SSTL (DC coupled)                                                                                                                            |    |

| 4.1.9 LVDS (AC coupled)                                                                                                                            | 22 |

| 4.1.10 LVPECL (AC coupled)                                                                                                                         |    |

| 4.2 Termination of Output Driver of Au5410 for Various Load Configurations                                                                         |    |

| 4.2.1 Au5410 Output ODR Termination for AC Coupled mode                                                                                            |    |

| 4.2.2 Au5410 Output ODR Termination for DC Coupled mode                                                                                            |    |

| 4.2.3 CMOS (Capacitive load)                                                                                                                       |    |

| 4.3 Power Considerations                                                                                                                           |    |

| <ul> <li>4.4 Core Current in XO Mode</li> <li>4.5 Parameter Measurement Information</li> </ul>                                                     |    |

| 4.5 Parameter Measurement information                                                                                                              |    |

| 4.5.2 Skew and Input to Output Delay                                                                                                               |    |

| 4.5.3 Rise and Fall Times                                                                                                                          |    |

| 4.5.4 Isolation                                                                                                                                    |    |

| 5 Thermal Information                                                                                                                              |    |

| 6 HOT Swap Recommendations                                                                                                                         |    |

| •                                                                                                                                                  |    |

| 6.1 Introduction                                                                                                                                   |    |

| <ul><li>6.2 Typical Differential Input Clock</li><li>6.3 Input Clock Termination with Hot Swap Protection</li></ul>                                |    |

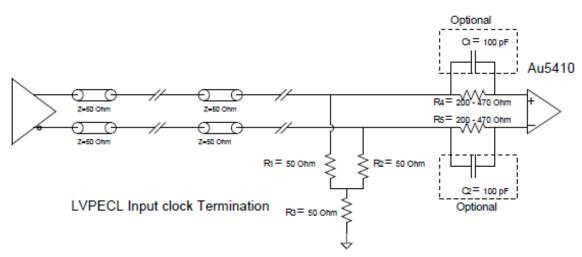

| 6.3.1 LVPECL Termination Example                                                                                                                   |    |

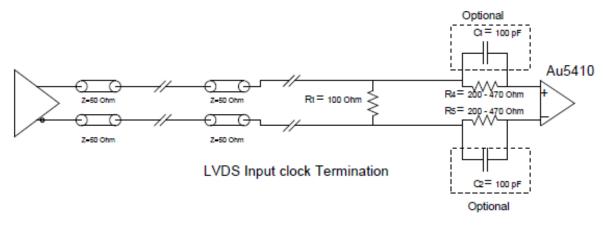

| 6.3.2 LVDS Input Clock Termination Example                                                                                                         |    |

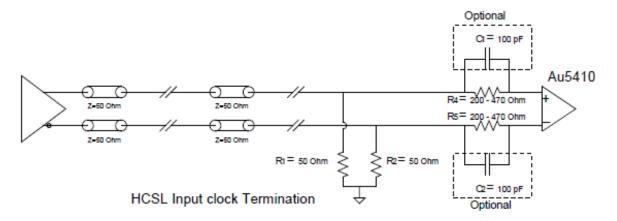

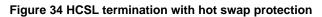

| 6.3.3 HCSL Input Clock Termination Example                                                                                                         |    |

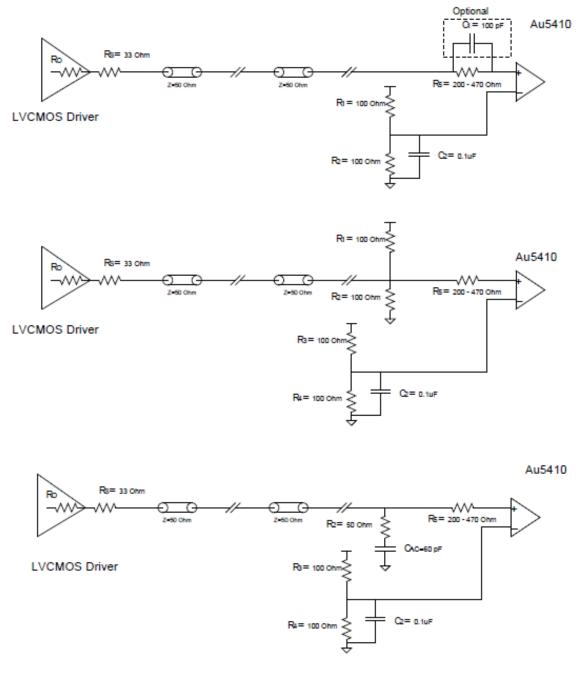

| 6.3.4 LVCMOS Input Clock Termination with Hot Swap Protection                                                                                      |    |

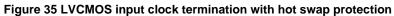

| 6.4 LVCMOS Output Clock Termination with Hot Swap Protection                                                                                       |    |

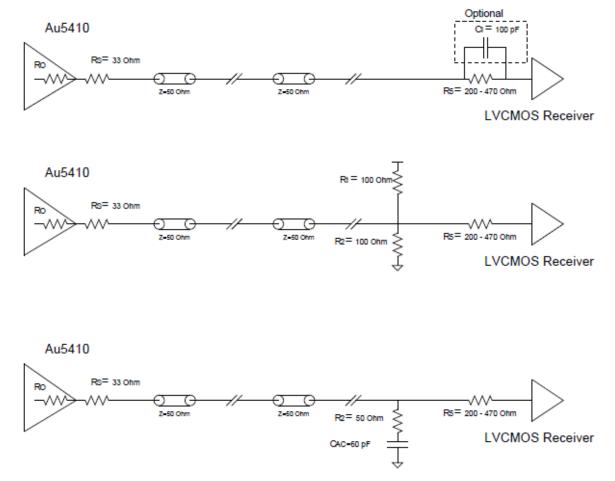

| 7 Operation in Multiple VDDO Supply Domains                                                                                                        |    |

| 8 Package Information                                                                                                                              |    |

|                                                                                                                                                    |    |

| 9 Ordering Information                                                                                                                             |    |

| 10 Revision History                                                                                                                                |    |

| 11 Trademarks                                                                                                                                      |    |

| 12 Contact Information                                                                                                                             | 39 |

|                                                                                                                                                    |    |

## **List of Tables**

| Table 1 Detailed Pin Description                      | 5 |

|-------------------------------------------------------|---|

| Table 2 Absolute Maximum Ratings                      | 7 |

| Table 3 Recommended Operating Supply and Temperatures | 7 |

| Table 4 DC Electrical Characteristics                 | 7 |

| Table 5 Input Clock Characteristics                   | 3 |

| Table 6 Output Clock Characteristics - LVCMOS         | ) |

| Table 7 Input Clock Selection 12                      | 2 |

| Table 8 Input versus Output Stages 12                 | 2 |

| Table 9 OE Functionality 12                           | 2 |

| Table 10 Thermal Metrics of Au5410 29                 | ) |

| Table 11 Ordering Information for Au5410 36           | 3 |

| Table 12 Revision History                             | 7 |

# List of Figures

| Figure 1 Functional Overview                                                                 | 1    |

|----------------------------------------------------------------------------------------------|------|

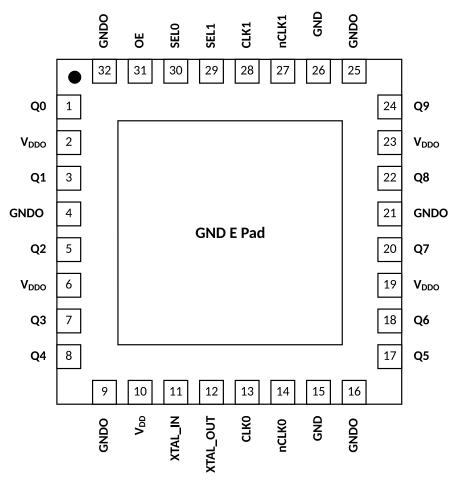

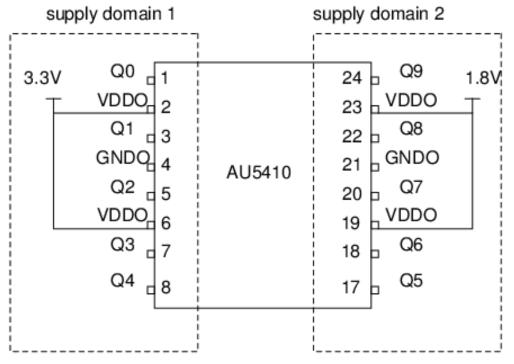

| Figure 2 Au5410 Buffer, LVCMOS output buffer Top View                                        | 5    |

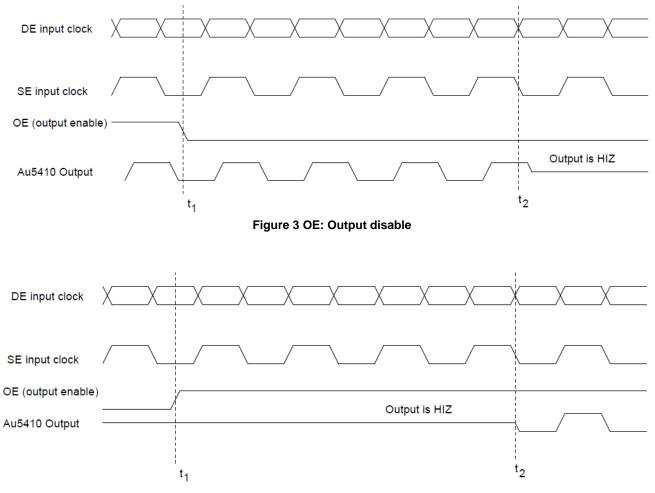

| Figure 3 OE: Output disable                                                                  | . 13 |

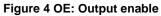

| Figure 4 OE: Output enable                                                                   | . 13 |

| Figure 5 AC coupling LVCMOS clock to Au5410                                                  | . 14 |

| Figure 6 AC coupling of LVCMOS clock with single 50 $\Omega$ resistor termination to ground  | . 15 |

| Figure 7 DC coupling of LVCMOS clock to Au5410 – configuration 1                             | . 16 |

| Figure 8 DC coupled LVCMOS input clock configuration – configuration 2                       | . 17 |

| Figure 9 DC coupled LVCMOS input clock with series RC termination – configuration 3          | . 17 |

| Figure 10: Direct coupling of LVCMOS clock to Au5410                                         | . 18 |

| Figure 11 Single ended LVCMOS input – configuration 1, AC coupling to crystal input          | . 19 |

| Figure 12 Single ended LVCMOS input – configuration 2, AC coupling to crystal input          | . 19 |

| Figure 13 Single ended LVCMOS input, DC coupling to crystal input                            | . 20 |

| Figure 14 Termination scheme for DC coupled LVDS                                             | . 20 |

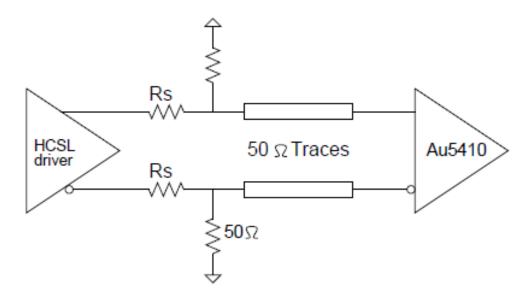

| Figure 15 Termination scheme for DC coupled HCSL                                             | . 20 |

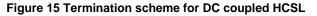

| Figure 16 Termination scheme for DC coupled LVPECL                                           | . 21 |

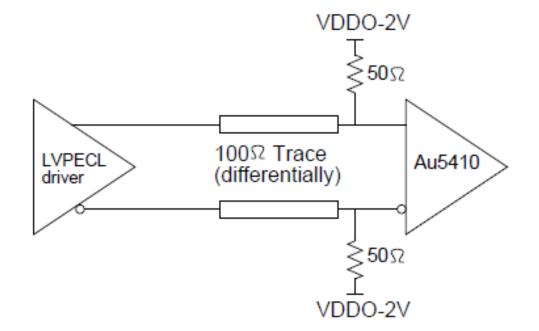

| Figure 17 Termination scheme for DC coupled LVPECL, Thevenin equivalent                      | . 21 |

| Figure 18 Example of input clock termination for SSTL clock                                  | . 22 |

| Figure 19 Termination scheme for AC coupled LVDS                                             | . 22 |

| Figure 20 Termination scheme for AC coupled LVPECL, Thevenin Equivalent                      | . 23 |

| Figure 21 AC coupling of LVCMOS clock with single 50 $\Omega$ resistor termination to ground | . 24 |

| Figure 22 DC coupling of LVCMOS output clock termination – configuration 1                   | . 24 |

| Figure 23 DC coupled LVCMOS output clock configuration – configuration 2                     | . 25 |

| Figure 24 DC coupled LVCMOS output clock with series RC termination – configuration 3        | . 26 |

| Figure 25 Typical application load                                                           | . 26 |

| Figure 26 Parameters related to differential input level                                     | . 27 |

| Figure 27 Parameter definitions of propagation delay and skew                                | . 27 |

| Figure 28 Parameter definitions related to rise and fall times                               | . 28 |

| Figure 29 Parameter definition of isolation                                                  | . 28 |

| Figure 30 Typical input differential clock                                                   | . 30 |

| Figure 31 LVPECL termination with hot swap protection                                        | . 30 |

| Figure 32 LVEPCL termination with hot swap protection                                        | . 31 |

| Figure 33 LVDS termination with hot swap protection                                          | . 31 |

| Figure 34 HCSL termination with hot swap protection                                          | . 31 |

| Figure 35 LVCMOS input clock termination with hot swap protection                            | . 32 |

| Figure 36 Different types of LVCMOS output clock termination with hot swap protection        | . 33 |

| Figure 37: Example of multi supply operation of Au5410                                       | . 34 |

| Figure 38 Au5410 32 pin QFN package dimensions                                               | . 35 |

## **1** Detailed Pin Description

#### **Table 1 Detailed Pin Description**

| Pin Name             | Pin Number | Functionality Au5410                                                |

|----------------------|------------|---------------------------------------------------------------------|

| Pin group: Clock out | put pins   |                                                                     |

| Q0                   | 1          | LVCMOS output 0                                                     |

| Q1                   | 3          | LVCMOS output 1                                                     |

| Q2                   | 5          | LVCMOS output 2                                                     |

| Q3                   | 7          | LVCMOS output 3                                                     |

| Q4                   | 8          | LVCMOS output 4                                                     |

| Q5                   | 17         | LVCMOS output 5                                                     |

| Q6                   | 18         | LVCMOS output 6                                                     |

| Q7                   | 20         | LVCMOS output 7                                                     |

| Q8                   | 22         | LVCMOS output 8                                                     |

| Q9                   | 24         | LVCMOS output 9                                                     |

| Pin group: Power pi  | าร         |                                                                     |

| VDDO                 | 2          | I/O power pins 3.3/2.5/1.8/1.5 V                                    |

| VDDO                 | 6          | I/O power pins 3.3/2.5/1.8/1.5 V                                    |

| VDDO                 | 19         | I/O power pins 3.3/2.5/1.8/1.5 V                                    |

| VDDO                 | 23         | I/O power pins 3.3/2.5/1.8/1.5 V                                    |

| VDD                  | 10         | Line supply 3.3/2.5/1.8 V - Au5410 can support 1.8 V on line supply |

| Pin Name               | Pin Number | Functionality Au5410                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GNDO                   | 9          | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| GND                    | 15         | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| GNDO                   | 16         | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| GNDO                   | 4          | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| GNDO                   | 21         | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| GND                    | 26         | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| GNDO                   | 25         | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| GNDO                   | 32         | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin group: Clock inpu  | t Pins     |                                                                                                                                                                                                                                                                                                                                                                                             |

| XTAL_IN                | 11         | Input for crystal. It can be over driven by an ac-coupled single ended clock<br>in crystal over drive mode.<br>In the external bypass mode, the max voltage at the pin needs to be 1.5 V.<br>If the driver is swinging to say 3.3 V rail, then a resistor divider is needed<br>on PCB to restrict the swing at XTAL_IN to 1.5 V<br>Cload supported 6 pF to 10 pF, frequency 8 MHz to 50 MHz |

| XTAL_OUT               | 12         | crystal oscillator pin                                                                                                                                                                                                                                                                                                                                                                      |

| CLK0                   | 13         | Non-inverting differential or single-ended primary input                                                                                                                                                                                                                                                                                                                                    |

| nCLK0                  | 14         | Inverting differential primary input                                                                                                                                                                                                                                                                                                                                                        |

| nCLK1                  | 27         | inverting differential secondary input                                                                                                                                                                                                                                                                                                                                                      |

| CLK1                   | 28         | Non-Inverting differential or single ended secondary input                                                                                                                                                                                                                                                                                                                                  |

| Pin group: Control Pir | is         |                                                                                                                                                                                                                                                                                                                                                                                             |

| SEL1                   | 29         | Input clock select 1                                                                                                                                                                                                                                                                                                                                                                        |

| SEL0                   | 30         | Input clock select 0                                                                                                                                                                                                                                                                                                                                                                        |

| OE                     | 31         | Output enable                                                                                                                                                                                                                                                                                                                                                                               |

## 2 Electrical Characteristics

#### Table 2 Absolute Maximum Ratings

| Description                                  | Conditions | Symbol          | Min  | Тур | Мах     | Units |

|----------------------------------------------|------------|-----------------|------|-----|---------|-------|

| Core Supply Voltage                          |            | V <sub>DD</sub> | -0.5 |     | 3.6     | V     |

| Output Supply Voltage                        |            | Vddo            | -0.5 |     | 3.6     | V     |

| Input voltage, All<br>Inputs, except XTAL_IN |            | V <sub>IN</sub> | -0.3 |     | VDD+0.3 | V     |

| XTAL_IN                                      |            | VIN             | -0.3 |     | 1.5     | V     |

| Storage temperature                          |            | TSTG            | -55  |     | 150     | °C    |

| Junction Temperature                         |            | TJ              |      |     | 125     | °C    |

Notes:

• Exceeding maximum ratings may shorten the useful life of the device.

• Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or at any other conditions beyond those indicated under the DC Electrical Characteristics is not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability or cause permanent device damage.

#### Table 3 Recommended Operating Supply and Temperatures

| Description           | Conditions      | Symbol         | Min       | Тур   | Max   | Units |

|-----------------------|-----------------|----------------|-----------|-------|-------|-------|

| Core supply voltage   |                 |                | 3.135     | 3.3   | 3.465 | V     |

|                       | V <sub>DD</sub> | 2.375          | 2.5       | 2.625 | V     |       |

|                       |                 | 1.71           | 1.8       | 1.89  | V     |       |

|                       |                 |                | 3.135     | 3.3   | 3.465 | V     |

|                       |                 | Vddo           | 2.375     | 2.5   | 2.625 | V     |

| Output supply voltage |                 | V DDO          | 1.6 1.8 2 | 2     | V     |       |

|                       |                 | 1.35           | 1.5       | 1.65  | V     |       |

| Ambient Temperature   |                 | T <sub>A</sub> | -40       | 27    | 85    | °C    |

#### **Table 4 DC Electrical Characteristics**

Unless otherwise specified:  $V_{DD} = 3.3 \text{ V} \pm 5\%$ , 2.5 V  $\pm 5\%$ ,  $V_{DDO} = 3.3 \text{ V} \pm 5\%$ , 2.5 V  $\pm 5\%$ , 1.8 V  $\pm 10\%$ , 1.5 V  $\pm 10\%$ , -40 °C  $\leq$  TA  $\leq$  85 °C, CLK0/1 driven differentially, input slew rate  $\geq 2$  V/ns. Typical values represent most likely parametric norms at  $V_{DD} = 3.3$  V,  $V_{DDO} = 3.3$  V,  $T_A = 25$  °C.

| Description                                                         | Conditions                                                                         | Symbol                               | Min     | Тур  | Max     | Units |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------|---------|------|---------|-------|

| Current Consumption                                                 |                                                                                    |                                      |         |      |         |       |

| Static current taken by<br>core supply when no<br>toggling          |                                                                                    | I <sub>CORE,STATIC</sub>             |         | 16   | 19.8    | mA    |

| Static current taken by<br>output driver supply<br>when no toggling |                                                                                    | I <sub>ODR,STATIC</sub>              |         | 3.5  | 4.2     | mA    |

| Current taken by core<br>supply, if XTAL is<br>enabled              | V <sub>DD</sub> = 3.3 V,<br>V <sub>DDO</sub> = 3.3 V,<br>F <sub>OSC</sub> = 25 MHz | Icore,static<br>,xtal <sup>(1)</sup> |         | 11.5 | 14      | mA    |

| Power Dissipation<br>Capacitance per output                         | $V_{DD} = 3.3 V,$<br>$V_{DDO} = 3.3 V,$<br>$F_{in} = 200 MHz$                      | C <sub>PD</sub> <sup>(1)</sup>       |         | 4    | 5.2     | pF    |

| Dynamic current taken by core supply                                | $V_{DD} = 3.3 V,$<br>$V_{DDO} = 3.3 V,$<br>$F_{in} = 100 MHz$                      | Icore, dyn                           |         | 1.3  | 1.56    | mA    |

| Input Control Pin Chara                                             | cteristic                                                                          |                                      |         |      |         |       |

| High level input voltage                                            |                                                                                    | VIH                                  | 0.7*VDD |      | VDD     | V     |

| Low level input voltage                                             |                                                                                    | VIL                                  | GND     |      | 0.3*VDD | V     |

| Description              | Conditions                | Symbol                | Min | Тур | Max | Units |

|--------------------------|---------------------------|-----------------------|-----|-----|-----|-------|

| High level input current | $V_{IH} = V_{DD} = 3.3 V$ | Ін                    |     | 30  | 50  | uA    |

| Low level input current  |                           | IIL                   | -20 | 0.1 |     | uA    |

| Pull down resistance     |                           | R <sub>PULLDOWN</sub> |     | 200 |     | KΩ    |

| Input capacitance        |                           | CIN                   |     | 2   |     | pF    |

Notes:

1. Specification is guaranteed by characterization and is not tested in production

#### **Table 5 Input Clock Characteristics**

Unless otherwise specified:  $V_{DD} = 3.3 \text{ V} \pm 5\%$ , 2.5 V  $\pm 5\%$ ,  $V_{DDO} = 3.3 \text{ V} \pm 5\%$ , 2.5 V  $\pm 5\%$ , 1.8 V  $\pm 10\%$ , 1.5 V  $\pm 10\%$ , -40 °C  $\leq$  TA  $\leq$  85 °C, CLK0/1 driven differentially, input slew rate  $\geq 2$  V/ns. Typical values represent most likely parametric norms at  $V_{DD} = 3.3$  V,  $V_{DDO} = 3.3$  V,  $T_A = 25$  °C.

| Parameter                                                                                          | Test Condition                                                                                                                                                              | Symbol                 | Min  | Тур | Max                   | Unit |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|-----------------------|------|

| DC Characteristics of u                                                                            | niversal input clock pins                                                                                                                                                   |                        |      |     | · · · · ·             |      |

| High level input current                                                                           | V <sub>IH</sub> = V <sub>DD</sub> = 3.465 V                                                                                                                                 | Ін                     |      |     | 650                   | uA   |

| Low level input current                                                                            |                                                                                                                                                                             | IL                     | -650 |     |                       | uA   |

| Pull up or pull down resistor on CLK0/1                                                            |                                                                                                                                                                             | R <sub>PULLUP_PU</sub> |      | 7.5 |                       | KΩ   |

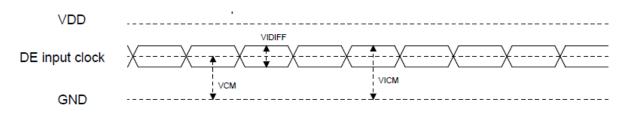

| Differential Input<br>Voltage Swing (peak to<br>peak) <sup>(1)</sup>                               |                                                                                                                                                                             | Vidiff                 | 0.15 |     | 1.3                   | V    |

| Differential Input<br>Common Mode<br>Voltage <sup>(2)</sup>                                        | VIDIFF = 150 mV                                                                                                                                                             | VICM                   | 0.25 |     | V <sub>DD</sub> -0.85 | V    |

| Single Ended Input<br>High Voltage <sup>(2)</sup>                                                  | Inverting differential input held at VDD/2, $V_{DD} = 3.3 V$                                                                                                                | VIHSE                  | 2    |     | V <sub>DD</sub> +0.3  | V    |

|                                                                                                    | Inverting differential input held at VDD/2, $V_{DD} = 2.5 V$                                                                                                                |                        | 1.6  |     | V <sub>DD</sub> +0.3  | V    |

| Single Ended Input Low Voltage <sup>(2)</sup>                                                      | Inverting differential input held at VDD/2, $V_{DD} = 3.3 V$                                                                                                                | VILSE                  | -0.3 |     | 1.3                   | V    |

|                                                                                                    | Inverting differential input held at VDD/2, $V_{DD} = 2.5 V$                                                                                                                |                        | -0.3 |     | 0.9                   | V    |

| AC Characteristics of u                                                                            | niversal input clock pins                                                                                                                                                   |                        |      |     | •                     |      |

| Input slew rate                                                                                    | 20% to 80%                                                                                                                                                                  | ΔVi/ΔT                 |      | 2   |                       | V/ns |

| Input Capacitance                                                                                  | Single ended                                                                                                                                                                | CIN                    | _    | 700 | —                     | fF   |

| Input Frequency Range                                                                              | LVDS and LVPECL outputs                                                                                                                                                     | f <sub>IN</sub>        | _    | _   | 250                   | MHz  |

|                                                                                                    | HCSL outputs                                                                                                                                                                |                        | _    | _   | 250                   | MHz  |

|                                                                                                    | LVCMOS outputs                                                                                                                                                              |                        | _    | _   | 250                   | MHz  |

| Input duty cycle, such<br>that output duty cycle is<br>equal to input duty<br>cycle <sup>(5)</sup> | The pass condition for<br>the measurement is<br>that output duty cycle is<br>within ±5% of input duty<br>cycle. The input clock<br>amplitude is same as<br>LVPECL standard. | IDC                    | 40   |     | 60                    | %    |

| Mux isolation clk0 to clk1 <sup>(3)</sup>                                                          | Foffset > 50 KHz,<br>Pclkin = 0 dBm,<br>Fclkin0 = 156.25 MHz                                                                                                                | ISO <sub>MUX</sub>     |      | -85 |                       | dBc  |

| Crystal Characteristic                                                                             | •                                                                                                                                                                           | •                      |      |     |                       |      |

| Parameter                                                | Test Condition                                                                                                                          | Symbol              | Min | Тур         | Мах | Unit |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-------------|-----|------|

| Equivalent series resistance                             |                                                                                                                                         | ESR                 |     | 35          | 60  | Ω    |

| load capacitance                                         |                                                                                                                                         | CL                  | 6   | 8           | 10  | pF   |

| Shunt Capacitance                                        |                                                                                                                                         | Co                  |     | 2           | 3   | pF   |

| Drive level                                              |                                                                                                                                         |                     |     | 100         | 200 | uW   |

| Mode of oscillation                                      |                                                                                                                                         |                     |     | fundamental |     |      |

| Supported crystal frequency range <sup>(3)</sup>         |                                                                                                                                         | Frequency           | 8   |             | 50  | MHz  |

| Maximum swing level<br>on XTAL_IN/<br>XTAL_OUT pins      | Bypass mode                                                                                                                             | V <sub>max</sub>    |     |             | 1.5 | V    |

| Fosc = 8 MHz                                             | Settling time required                                                                                                                  |                     |     | 14          |     | ms   |

| F <sub>osc</sub> = 25, 50 MHz                            | for output in crystal<br>mode                                                                                                           | t <sub>settle</sub> |     | 8           |     | ms   |

|                                                          | V <sub>DDO</sub> = 3.3 V<br>Slew Rate > 2 V/ns<br>Fin = 48 MHz                                                                          |                     |     | 100         |     | fs   |

| XO bypass AC coupled mode additive jitter <sup>(3)</sup> | V <sub>DDO</sub> = 2.5 V<br>Slew Rate > 2 V/ns<br>Fin = 48 MHz                                                                          | tjit                |     | 115         |     | fs   |

|                                                          | V <sub>DDO</sub> = 1.8 V<br>Slew Rate > 2 V/ns<br>Fin = 48 MHz                                                                          |                     |     | 230         |     | fs   |

| Additive jitter <sup>(3)</sup>                           | RMS, integration BW<br>12 KHz to 5 MHz,<br>$F_{crystal} = 25$ MHz.<br>Crystal input select<br>Measured at<br>$V_{DD} = V_{DDO} = 2.5$ V | tjit                |     | 155         |     | fs   |

Notes:

1. Inverting differential input clock pin biased at VDD/2

2. Input common mode defined as  $V_{IH}$  (see Figure 26)

3. Specification is guaranteed by characterization and is not tested in production

4. If the input clock is initially absent when the chip is just powered up, it will take at least 2 falling edge of clock cycles for the output to appear. Therefore, the buffer level translates DC only after it sees two consecutive falling edge of input clock

5. Output duty cycle equals input duty cycle. ATE measurement done with 80% on time and 20% off time waveform to make sure that output duty cycle is equal to input duty cycle even with skewed input duty cycle.

| Parameter                 | Test Condition                                           | Symbol          | Min  | Тур | Max | Unit |

|---------------------------|----------------------------------------------------------|-----------------|------|-----|-----|------|

| Maximum output            | Universal clock input                                    | Fout            |      |     | 250 | MHz  |

| frequency                 | XTAL <sup>(1)</sup>                                      |                 |      |     | 50  | MHz  |

|                           | For Fin ≤ 200 MHz                                        |                 | 45   |     | 55  | %    |

| Output duty cycle         | For<br>200 MHz < Fin < 250 MHz                           | Odc             | 40   |     | 60  |      |

|                           | $V_{DDO} = 3.3 \pm 5\%$ , 12 mA pull down current        |                 | 2.6  |     |     | V    |

|                           | $V_{DDO} = 2.5 \pm 5\%$ , 8 mA pull down current         |                 | 1.8  |     |     | V    |

| Output high level voltage | $V_{DDO} = 1.8 V \pm 200 mV,$<br>2 mA pull down current  | Voн             | 1.2  |     |     | V    |

|                           | $V_{DDO} = 1.5 V \pm 150 mV$ ,<br>2 mA pull down current |                 | 0.95 |     |     | V    |

| Output low level voltage  | $V_{DDO} = 3.3 \pm 5\%$ , 12 mA pull up current          | V <sub>OL</sub> |      |     | 0.5 | V    |

#### **Table 6 Output Clock Characteristics - LVCMOS**

| Parameter                                                                                | Test Condition                                                                                                                                                                        | Symbol           | Min | Тур | Max  | Unit  |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|------|-------|

|                                                                                          | $V_{DDO} = 2.5 \pm 5\%$ , 8 mA pull                                                                                                                                                   |                  |     |     | 0.5  | V     |

|                                                                                          | up current<br>$V_{DDO} = 1.8 \text{ V} \pm 200 \text{ mV},$                                                                                                                           |                  |     |     |      |       |

|                                                                                          | 2 mA pull up current                                                                                                                                                                  |                  |     |     | 0.4  | V     |

|                                                                                          | $V_{DDO} = 1.5 V \pm 150 mV$ ,<br>2mA pull up current                                                                                                                                 |                  |     |     | 0.35 | V     |

|                                                                                          | V <sub>DDO</sub> = 3.3 V                                                                                                                                                              |                  |     | 15  |      | Ω     |

| Effective output<br>impedance, for maximum                                               | V <sub>DDO</sub> = 2.5 V                                                                                                                                                              | R <sub>out</sub> |     | 18  |      | Ω     |

| slice strength                                                                           | V <sub>DDO</sub> = 1.8 V                                                                                                                                                              | · vou            |     | 23  |      | Ω     |

|                                                                                          | V <sub>DDO</sub> = 1.5 V                                                                                                                                                              |                  |     | 28  |      | Ω     |

|                                                                                          | V <sub>DDO</sub> = 3.465 V                                                                                                                                                            |                  |     | 40  |      | ps    |

| Output skew (1)                                                                          | $V_{DDO} = 2.5V$                                                                                                                                                                      | t <sub>sk</sub>  |     | 35  |      | ps    |

|                                                                                          | $V_{DDO} = 1.62 V$                                                                                                                                                                    |                  |     | 31  |      | ps    |

| Time for output enable or                                                                | V <sub>DDO</sub> = 1.35 V                                                                                                                                                             |                  |     | 36  |      | ps    |

| disable <sup>(1)</sup>                                                                   |                                                                                                                                                                                       | t <sub>en</sub>  |     |     | 4    | cycle |

|                                                                                          | $\label{eq:V_DDO} \begin{array}{l} V_{\text{DDO}} = 3.465 \text{ V}, \text{ PCB trace} \\ \text{of 5 inch, 10 pF capacitor} \\ \text{AC coupled 50 } \Omega \text{ load} \end{array}$ |                  |     | 1.4 |      | ns    |

| Input to clock edge to                                                                   | $V_{DDO}$ = 2.5 V, PCB trace of<br>5 inch, 10 pF capacitor AC<br>coupled 50 $\Omega$ load                                                                                             | • t <sub>d</sub> |     | 1.5 |      | ns    |

| output clock edge delay                                                                  | $V_{\text{DDO}} = 1.62 \text{ V}, \text{ PCB trace}$<br>of 5 inch, 10 pF capacitor<br>AC coupled 50 $\Omega$ load                                                                     | <sup>L</sup> d   |     | 2   |      | ns    |

|                                                                                          | $V_{DDO}$ = 1.35 V, PCB trace<br>of 5 inch, 10 pF capacitor<br>AC coupled 50 $\Omega$ load                                                                                            |                  |     | 2.5 |      | ns    |

|                                                                                          | V <sub>DDO</sub> = 3.465 V<br>Slew rate (Au5410)<br>≥ 2 V/ns                                                                                                                          |                  |     | 21  |      | fs    |

| Additive jitter <sup>(1)</sup>                                                           | $V_{DDO} = 2.5 V$<br>Slew rate<br>(Au5410) $\ge 2 V/ns$                                                                                                                               |                  |     | 37  |      | fs    |

|                                                                                          | V <sub>DDO</sub> = 1.62 V<br>Slew rate<br>(Au5410) ≥ 2 V/ns                                                                                                                           | t <sub>jit</sub> |     | 87  |      | fs    |

|                                                                                          | V <sub>DDO</sub> = 1.35 V<br>Slew rate (Au5410)<br>≥ 2 V/ns                                                                                                                           |                  |     | 233 |      | fs    |

|                                                                                          | Output rise time 20% to 80%<br>Load cap 5 pF, $V_{DDO} = 3.3 \text{ V}$ , AC coupled 50 $\Omega$ load                                                                                 |                  |     |     | 605  | ps    |

| Rise time <sup>(1)</sup>                                                                 | Output rise time 20% to 80%<br>Load cap 5 pF, $V_{DDO}$ = 2.5 V, AC coupled 50 $\Omega$ load                                                                                          |                  |     |     | 605  | ps    |

| Kise time <sup>(1)</sup>                                                                 | Output rise time 20% to 80%<br>Load cap 5 pF, $V_{DDO} = 1.62$ V, AC coupled 50 $\Omega$ load                                                                                         | t <sub>R</sub>   |     |     | 605  | ps    |

|                                                                                          | Output rise time 20% to 80%<br>Load cap 5 pF, $V_{DDO} = 1.35$ V, AC coupled 50 $\Omega$ load                                                                                         |                  |     |     | 605  | ps    |

| Fall time <sup>(1)</sup> Output fall time 20% to 80%<br>Load cap 5 pF, $V_{DDO} = 3.3 V$ |                                                                                                                                                                                       | t <sub>F</sub>   |     |     | 605  | ps    |

| Parameter | Test Condition                                                   | Symbol | Min | Тур | Max | Unit |

|-----------|------------------------------------------------------------------|--------|-----|-----|-----|------|

|           | Output fall time 20% to 80%<br>Load cap 5 pF, $V_{DDO} = 2.5 V$  |        |     |     | 605 | ps   |

|           | Output fall time 20% to 80%<br>Load cap 5 pF, $V_{DDO} = 1.62 V$ |        |     |     | 605 | ps   |

|           | Output fall time 20% to 80%<br>Load cap 5 pF, $V_{DDO} = 1.35 V$ |        |     |     | 605 | ps   |

Notes:

1. Specification is guaranteed by characterization and is not tested in production

## **3 Functional Description**

The Au5410 is a 10-output differential clock fan out buffer with low additive jitter that can operate up to 250 MHz. It features a 3:1 input multiplexer with an optional crystal oscillator input and ten LVCMOS output. The input selection and output buffer modes are controlled via pin strapping. The device is offered in a 32-pin QFN package.

## 3.1 VDD and VDDO Power Supplies

The Au5410 has separate 3.3 V/2.5 /1.8 V core (VDD) and 3.3 V/2.5 V/1.8 V/1.5 V output power supply ( $V_{DDO}$ ). Output supply operation at 2.5 V/1.8 V/1.5 V enables lower power consumption and output-level compatibility with 2.5 V/1.8 V/1.5 V receiver devices. The output levels LVCMOS (VOH) is referenced to its respective  $V_{DDO}$  supply.

### 3.2 Clock Inputs

The input clock can be selected from primary universal clock input, secondary universal clock input, or Xin. Clock input selection is controlled using the SEL[1:0] inputs as shown in Table 7

| SEL[1] | SEL[0] | Selected Clock                                  |

|--------|--------|-------------------------------------------------|

| 0      | 0      | CLK0                                            |

| 0      | 1      | CLK1                                            |

| 1      | 0      | Crystal<br>Or<br>Crystal bypass AC coupled mode |

| 1      | 1      | Crystal bypass DC coupled mode                  |

| Table 7 | ' Input | <b>Clock Selection</b> |  |

|---------|---------|------------------------|--|

|---------|---------|------------------------|--|

## 3.3 Clock States (Input vs Output States)

#### Table 8 Input versus Output Stages

| State of Selected Clock input | Output State |

|-------------------------------|--------------|

| Inputs are floating           | Logic low    |

| Inputs are logic low          | logic low    |

| Inputs are logic high         | logic high   |

### 3.4 Output Enable

Pulling OE to LOW, forces the outputs to the high-impedance state after the four falling edge of the input signal. The outputs remain in the high-impedance state as long as OE is LOW. The OE signal is internally synchronized to the selected input clock. This allows disabling the output clock at the falling edge of input clock in a glitch free manner.

When OE goes from low to high, the output clock is enabled within a time delay td, where td is given by the following equation.

$t_{d,refout en} = 0.5n + 4 * T_{in}$ . Tin is the time period of the input clock.

#### Table 9 OE Functionality

| OE | Output State   |

|----|----------------|

| 0  | Disabled (HIZ) |

| 1  | Enabled        |

## **4** Application Information

## 4.1 Driving the Clock Inputs

The Au5410 has two universal clock inputs (CLK0/nCLK0 and CLK1/nCLK1) Au5410 can accept 3.3 V/2.5 V LVPECL, LVDS, CML, SSTL, and other differential and single-ended signals that meet input common mode, slew rate and swing requirements specified in the Electrical Characteristics. The Au5410 supports a wide common mode voltage range and input signal swing

To achieve the best possible phase noise and jitter performance, it is mandatory for the input to have high slew rate of 2 V/ns (differential) or higher. Driving the input with a lower slew rate will degrade the noise floor and jitter.

It is recommended to drive the input signal differentially for better slew rate and jitter. The user can also drive a single ended clock. If the user is driving the single ended clock signal on say CLK0, then nCLK0 pin need to be connected to a 0.1 uF capacitor on the PCB.

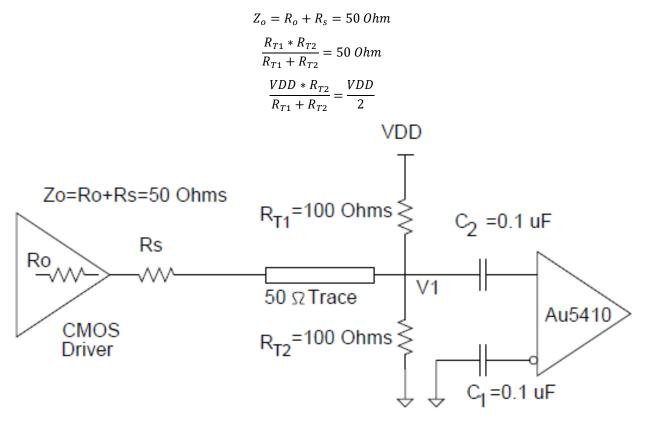

## 4.1.1 Driving Clock Inputs with LVCMOS Driver (AC coupled)

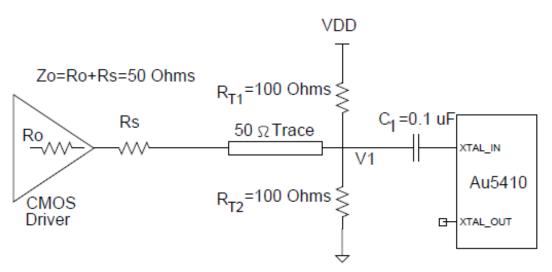

Figure 5 shows how a differential input can be wired to accept LVCMOS single ended levels in AC coupled mode. The bypass capacitor (C1) is used to help filter noise on the DC bias on the inverting pin of the clock input. This bypass should be located as close to the input pin as possible. Two resistors  $R_{T1}$  and  $R_{T2}$  set the common mode voltage at the output of the LVCMOS driver to VDD/2. This prevents average DC leakage current from the LVCMOS driver and avoids unnecessary power dissipation.

For example, if the input clock is driven from a single-ended 2.5 V LVCMOS driver and the DC offset (or swing center) of this signal is 1.25 V, the  $R_{T1}$  and  $R_{T2}$  values should be adjusted to set the V1 at 1.25 V. This configuration requires that the sum of the output impedance of the driver (Ro) and the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the input will attenuate the signal in half. This can be done in the following way. First,  $R_{T1}$  and  $R_{T2}$  in parallel should equal the transmission line impedance. For most 50  $\Omega$  applications,  $R_{T1}$  and  $R_{T2}$  can be 100  $\Omega$ .

The inverting differential input can be connected to a 0.1 uF bypass capacitor. This pin is biased internally to a voltage close to VDD/2.

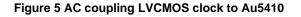

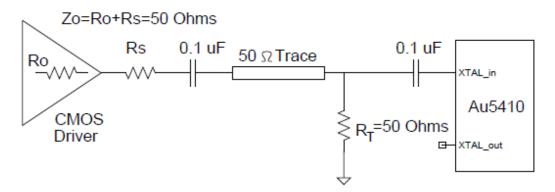

Another variant of the AC coupling of LVCMOS input clock is shown in Figure 6. We use single termination resistor of 50  $\Omega$  to ground. A 0.1 uF AC coupling capacitor is connected in series with the LVCMOS clock source to prevent DC leakage current.

$$Z_o = R_o + R_s = 50 Ohm$$

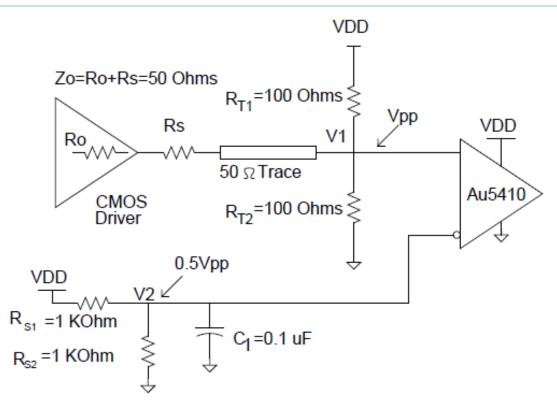

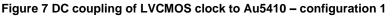

#### 4.1.2 Driving Clock Inputs with LVCMOS Driver (DC coupled)

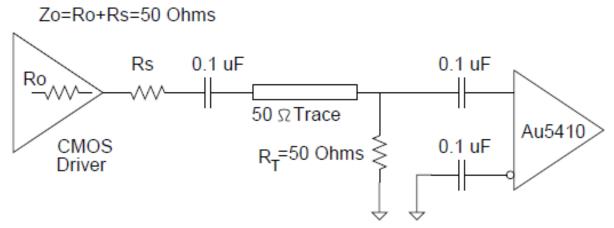

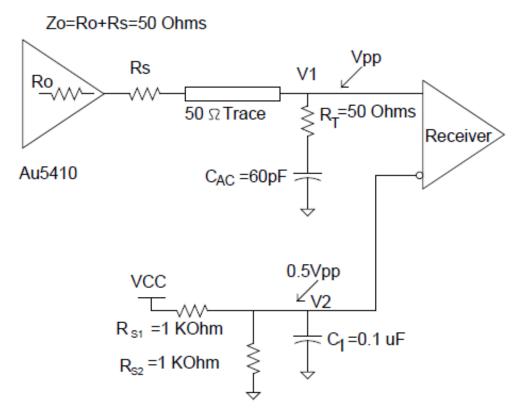

Figure 7 shows how a differential input can be wired to accept LVCMOS single ended clock signals in DC coupled mode. The reference voltage V1 = VDD/2 is generated by the bias resistors  $R_{S1}$  and  $R_{S2}$ . The bypass capacitor (C1) is used to help filter noise on the DC bias. This bias circuit should be located as close to the input pin as possible. The ratio of  $R_{S1}$  and  $R_{S2}$  might need to be adjusted to position the bias voltage V2 in the center of the input voltage swing. Typical values of bias circuit resistance are  $R_{S1} = 1 \text{ K}\Omega$  and  $R_{S2} = 1 \text{ K}\Omega$

$$Z_{o} = R_{o} + R_{s} = 50 \text{ Ohm}$$

$$\frac{VDD * R_{s2}}{R_{s1} + R_{s2}} = \frac{VDD}{2}$$

$$\frac{R_{T1} * R_{T2}}{R_{T1} + R_{T2}} = 50 \text{ Ohm}$$

$$\frac{VDD * R_{T2}}{R_{T1} + R_{T2}} = \frac{VDD}{2}$$

For example, if the input clock is driven from a single-ended 2.5 V LVCMOS driver and the DC offset (or swing center) of this signal is 1.25 V, the R<sub>S1</sub> and R<sub>S2</sub> values should be adjusted to set the V2 at 1.25 V. The values below are for when both the single ended swing and VDD are at the same voltage.

This configuration requires that the sum of the output impedance of the driver (Ro) and the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the input will attenuate the signal in half. This can be done in one of two ways. First,  $R_{T1}$  and  $R_{T2}$  in parallel should equal the transmission line impedance. For most 50  $\Omega$  applications,  $R_{T1}$  and  $R_{T2}$  can be 100  $\Omega$ . The values of the resistors can be increased to reduce the loading for slower and weaker LVCMOS driver.

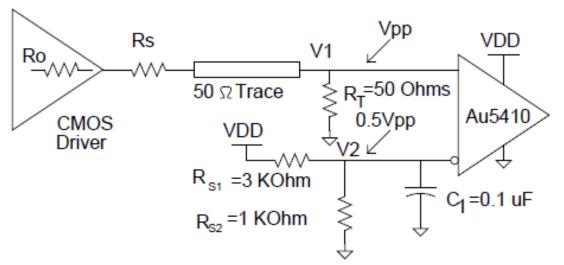

Figure 8 shows a second input clock configuration where  $R_{T1}$ ,  $R_{T2}$  are removed and replaced with a 50  $\Omega$  termination resistor RT to ground. It is possible that LVCMOS driver (or clock source) may not be able to drive 50  $\Omega$  load in DC coupled mode. The user can use series RC termination to overcome this limitation. The design equations for the input clock configuration shown in Figure 8 is given below

$$Z_o = R_o + R_s = 50 Ohm$$

$$\frac{VDD * R_{s2}}{R_{s1} + R_{s2}} = \frac{Vpp}{2}$$

The LVCMOS single ended clock input with series RC termination near the buffer is shown in Figure 9. There is a single termination resistor RT which is connected to ground through a capacitor  $C_{AC}$ . The value of series capacitor is given by a formula.

$C_{AC} \geq \frac{3T_D}{500}$ ,  $T_D$  is the transmission line delay

## Zo=Ro+Rs=50 Ohms

Figure 8 DC coupled LVCMOS input clock configuration – configuration 2

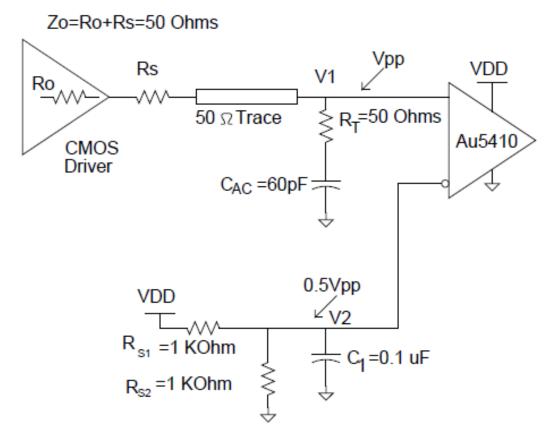

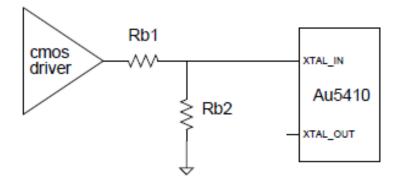

Figure 9 DC coupled LVCMOS input clock with series RC termination – configuration 3 For low frequencies we can direct couple the LVCMOS clock to Au5410 input clock pin as shown below.

Figure 10: Direct coupling of LVCMOS clock to Au5410

### 4.1.3 Driving XTAL\_IN with LVCMOS Driver (AC coupled)

The crystal input XTAL\_IN can be overdriven with single ended clock (LVCMOS driver or one side of a differential driver). The peak swing at XTAL\_IN should be limited to 1.5 V. The XTAL\_OUT pin, in this case can be floating. The SEL1, SEL0 should be 2'b10. The maximum voltage at XTAL\_IN should not exceed1.5 V and minimum voltage should not go below -0.3 V. The slew rate at XTAL\_IN should be greater than 0.2 V/ns.

For 3.3 V LVCMOS inputs, the amplitude must be reduced from full swing to at least half the swing in order to prevent signal interference with the power rail and to reduce internal noise. Figure 11 shows an example of the interface diagram for a high speed 3.3 V LVCMOS driver. This configuration requires that the sum of the output impedance of the driver (Ro) and the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the crystal input will attenuate the signal in half. This can be done in one of two ways. First,  $R_{T1}$  and  $R_{T2}$  in parallel should equal the transmission line impedance. For most 50  $\Omega$  applications,  $R_{T1}$  and  $R_{T2}$  can be 100  $\Omega$ .

$$Z_o = R_o + R_s = 50 \ Ohm$$

$$\frac{R_{T1} * R_{T2}}{R_{T1} + R_{T2}} = 50 \ Ohm$$

$$\frac{VDD * R_{T2}}{R_{T1} + R_{T2}} = \frac{VDD}{2}$$

For both the AC coupled configurations, the maximum peak to peak swing before the ac coupling capacitor is 1.65V. The maximum DC bias voltage of XTAL\_IN is 0.675V. Therefore the maximum swing at the XTAL\_IN pin is given by the equation given below.

$V_{swing,pk,XTAL_{IN}} = 0.675 + 0.5 * 1.65 = 1.5V$

Figure 11 Single ended LVCMOS input – configuration 1, AC coupling to crystal input

Figure 12 shows a second input clock configuration where RT1, RT2 are removed and replaced with a 50  $\Omega$  termination resistor RT to ground. A 0.1 uF is in series with the CMOS driver to prevent any DC leakage current.

Figure 12 Single ended LVCMOS input – configuration 2, AC coupling to crystal input

## 4.1.4 Driving XTAL\_IN with LVCMOS Driver (DC coupled)

The crystal input XTAL\_IN can be overdriven with single ended clock as shown in Figure 13, in DC coupled mode. The peak swing at XTAL\_IN should be limited to 1.5 V. The XTAL\_OUT pin, in this case can be floating. The SEL1, SEL0 should be 2'b11. If the LVCMOS driver is on higher supply, say 3.3 V, use a resistor divider on the PCB to scale down the peak output voltage to 1.5 V.

#### Figure 13 Single ended LVCMOS input, DC coupling to crystal input

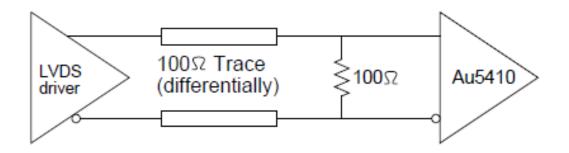

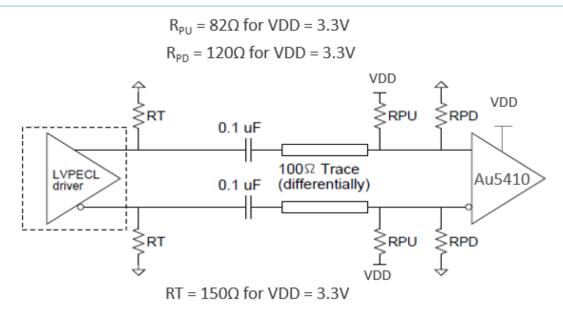

#### 4.1.5 LVDS (DC coupled)

Terminate with a differential 100  $\Omega$  as close to the receiver as possible. This is shown in Figure 14.

Figure 14 Termination scheme for DC coupled LVDS

#### 4.1.6 HCSL (DC coupled)

Termination resistor is 50  $\Omega$  to ground, close to the output driver. A series resistance Rs is sometimes used to limit the overshoot during fast transients. The termination scheme is shown in Figure 15.

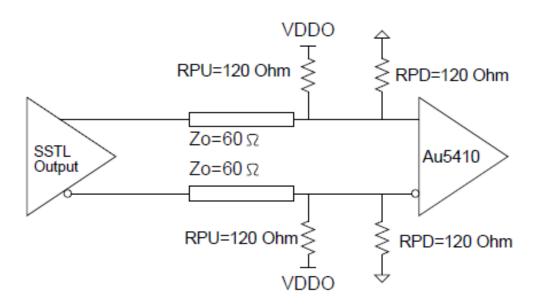

#### 4.1.7 LVPECL (DC coupled)

For DC coupled operation, the 50  $\Omega$  termination resistors are placed close to the receiver. The termination resistors are biased with a voltage source VTT.

$$V_{TT} = V_{DDO} - 2V.$$

This termination scheme is shown in Figure 16. Alternatively, the user can also implement a Thevenin equivalent of VTT using a resistor divider. This scheme and the values of the resistors in the resistor divider are given in Figure 17.

Figure 16 Termination scheme for DC coupled LVPECL

The design equations for the LVPECL Thevenin equivalent termination are given below.

$$\frac{R_{PD} * R_{PU}}{R_{PD} + R_{PU}} = 50\Omega$$

$$\frac{R_{PD} * VDDO}{R_{PD} + R_{PU}} = VDDO - 2V$$

### 4.1.8 SSTL (DC coupled)

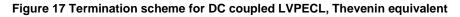

The SSTL input clock configuration is shown in Figure 18. The transmission line impedance is 60  $\Omega$  in the application example given. Therefore, we use two 120  $\Omega$  resistors from VDDO to ground for biasing the clock input pins. The effective termination impedance in this case is 60  $\Omega$ .

Figure 18 Example of input clock termination for SSTL clock.

### 4.1.9 LVDS (AC coupled)

The load termination resistor should be placed before the AC coupling capacitors. The load termination resistor and the AC coupling capacitors should be placed close to the receiver. The termination scheme is shown in Figure 19.

Figure 19 Termination scheme for AC coupled LVDS

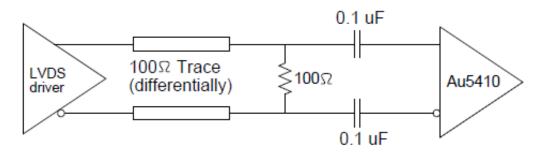

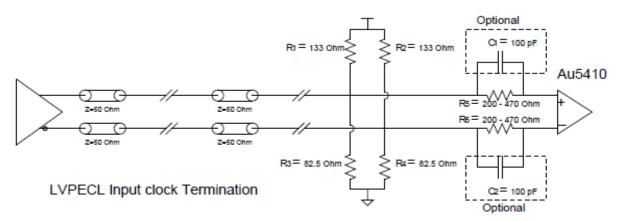

### 4.1.10 LVPECL (AC coupled)

The LVPECL should have a DC path to ground. So, the user must place a resistance  $R_T$ , close to the output driver. The LVPECL AC coupling and Thevenin equivalent VTT termination scheme is shown in Figure 20.

Figure 20 Termination scheme for AC coupled LVPECL, Thevenin Equivalent

The pull up resistance  $R_{PU}$  and pull down resistance  $R_{PD}$  sets the input common mode voltage for Au5410. The value of the input common mode voltage can be estimated by the equation given below

$$V_{ICM} = \frac{VDD * R_{PD}}{R_{PU+R_{PD}}} = \frac{3.3 * 120}{120 + 82} = 1.961V$$

The differential input common mode specification of Au5410 (from data sheet) is VDD -1.1 = 2.2 V, therefore the input common mode set by LVPECL AC coupled termination meets the Au5410 input common mode specification.

The LVPECL driver chip has resistance RT providing DC path for the output driver current in the LVPECL driver.

The effective load impedance at the input side of Au5410 (receiver side) is formed by parallel combination of  $R_{PU}$ ,  $R_{PD}$ .

The effective termination resistor value is given by the equation below

$$R_{termination} = \frac{R_{PU} * R_{PD}}{R_{PU} + R_{PD}} = \frac{120 * 82}{120 + 82} = 48.7\Omega$$

### 4.2 Termination of Output Driver of Au5410 for Various Load Configurations

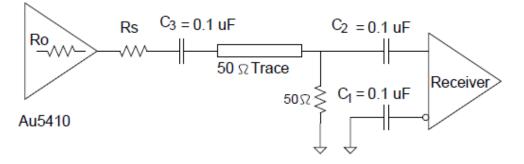

#### 4.2.1 Au5410 Output ODR Termination for AC Coupled mode

AC coupling of Au5410 LVCMOS output driver is shown in Figure 21. We use single termination resistor of 50  $\Omega$ s to ground. A 0.1 uF AC coupling capacitor is connected in series with the LVCMOS clock source to prevent DC leakage current. The receiver side is terminated with a single 50  $\Omega$  resistance to ground. The clock signal is then AC coupled to the receiver, in this example. C1 is a bypass capacitor that is used to suppress noise on the inverting differential input of the receiver.

$$Z_o = R_o + R_s = 50 \ Ohm$$

Figure 21 AC coupling of LVCMOS clock with single 50  $\Omega$  resistor termination to ground

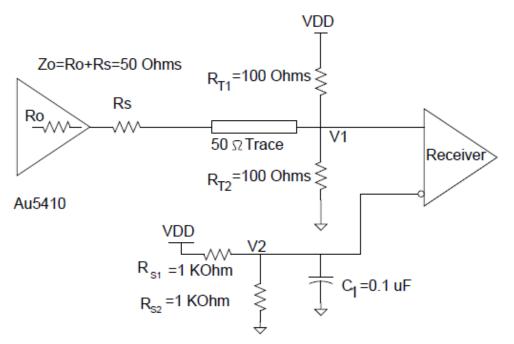

### 4.2.2 Au5410 Output ODR Termination for DC Coupled mode

Figure 22 shows how Au5410 LVCMOS output drive can be terminated to send clock signals in DC coupled mode. The reference voltage V1= VDD/2 is generated by the bias resistors  $R_{S1}$  and  $R_{S2}$ . The bypass capacitor (C<sub>1</sub>) is used to help filter noise on the DC bias. This bias circuit should be located as close to the input pin as possible. The ratio of  $R_{S1}$  and  $R_{S2}$  might need to be adjusted to position the bias voltage V2 in the center of the input voltage swing.

$$Z_o = R_o + R_s = 50 \text{ Ohm}$$

$$\frac{VDD * R_{s2}}{R_{s1} + R_{s2}} = \frac{VDD}{2}, \text{Typical value of } R_{s1} = R_{s2} = 1K\Omega$$

$$\frac{R_{T1} * R_{T2}}{R_{T1} + R_{T2}} = 50 \text{ Ohm, Typical value of } R_{T1} = R_{T2} = 100\Omega$$

$$\frac{VDD * R_{T2}}{R_{T1} + R_{T2}} = \frac{VDD}{2}$$

For example, if the Au5410 supply is 2.5 V then the DC offset (or swing center) of this signal is 1.25 V, the  $R_{S1}$  and  $R_{S2}$  values should be adjusted to set the V2 at 1.25 V. The values below are for when both the single ended swing and VDD are at the same voltage.

This configuration requires that the sum of the output impedance of the driver (Ro) and the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the input will attenuate the signal in half. This can be done in one of two ways. First,  $R_{T1}$  and  $R_{T2}$  in parallel should equal the transmission line impedance. For most 50  $\Omega$  applications,  $R_{T1}$  and  $R_{T2}$  can be 100  $\Omega$ . The values of the resistors can be increased to reduce the loading for slower and weaker LVCMOS driver.

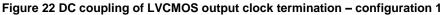

Figure 23 shows a second input clock configuration where  $R_{T1}$ ,  $R_{T2}$  are removed and replaced with a 50  $\Omega$  termination resistor  $R_T$  to ground. There will be DC leakage current from Au5410, for the output termination shown in Figure 23. The user can use series RC termination to overcome this limitation. The design equations for the input clock configuration shown in Figure 23 is given below

$Z_o = R_o + R_s = 50 \text{ Ohm}$   $\frac{VDD * R_{s2}}{R_{s1} + R_{s2}} = \frac{Vpp}{2} = \frac{VDD}{4}, Typical \text{ value of } R_{s1} = 3K\Omega, R_{s2} = 1K\Omega$

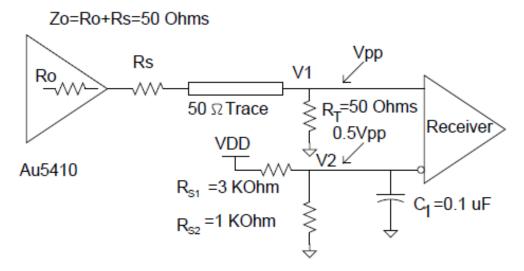

The Au5410 LVCMOS output driver termination with series RC termination near the buffer is shown in Figure 24. There is a single termination resistor RT which is connected to ground through a capacitor CAC. The value of series capacitor is given by a formula.

$C_{AC} \ge \frac{3T_D}{500}$ ,  $T_D$  is the transmission line delay

Typical value for  $C_{AC}$  is 60 pF, assuming delay of  $T_D = 200$  ps/inch and 5 inch input clock route length.

Figure 23 DC coupled LVCMOS output clock configuration – configuration 2

Figure 24 DC coupled LVCMOS output clock with series RC termination – configuration 3 The typical value of  $R_{s1}$  and  $R_{s2}$  in this case is 1 K $\Omega$  and that of  $C_{AC}$  is 60 pF.

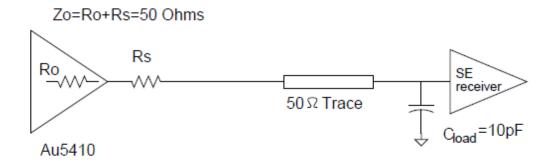

### 4.2.3 CMOS (Capacitive load)

The capacitive load can be driven as shown in figure below. Rs = 33  $\Omega$  for VDDO = 3.3 V.

#### Figure 25 Typical application load

### 4.3 **Power Considerations**

The following power consideration refers to the device-consumed power consumption only. The device power consumption is the sum of static power and dynamic power. The dynamic power usage consists of two components:

- Power used by the device as it switches states

- Power required to charge any output load. The output load can be capacitive-only or capacitive and resistive. Use the following formula to calculate the power consumption of the device:

$P_{DEV} = P_{STATIC} + P_{DYNAMIC} + P_{CLOAD}$

$$P_{STATIC} = I_{CORE\_STATIC} * VDD + I_{ODR,\_STATIC} * VDDO$$

$$P_{DYNAMIC} = I_{CORE\_DYNAMIC\_100MHZ} * VDD * \frac{F_{in}(units in MHz)}{100} + C_{PD} * 10 * F_{in} * VDDO^{2}$$

$$P_{CLOAD} = C_{LOAD} * 10 * F_{in} * VDDO^{2}$$

Let us calculate typical power dissipation for CLOAD of 2 pF at input clock of 100 MHZ. Assume that VDD = VDDO = 3.3 V.

$$P_{STATIC} = 16mA * 3.3V + 3.5mA * 3.3V = 64.35mW$$

$$P_{DYNAMIC} = 1.5mA * \frac{100}{100} * 3.3V + 4.0pF * 10 * 100MHz * 3.3V * 3.3V = 48.51 mW$$

$$P_{CLOAD} = 2pF * 10 * 100MHz * 3.3V * 3.3V = 21.78mW$$

$$P_{DEV} = 134.64mW$$

### 4.4 Core Current in XO Mode

The crystal mode standalone block current is measured in ATE. We can calculate total VDD core current in crystal mode, in typical condition using the below equation. The worst case VDD core current will be 14 mA, in crystal mode.

$I_{core\_crystal} = 8.5 + I_{xo\_standalone} = 11.5 mA$ , typical

#### 4.5 Parameter Measurement Information

#### 4.5.1 Differential Input Level

The parameter definitions related to differential input level is shown below.

Figure 26 Parameters related to differential input level

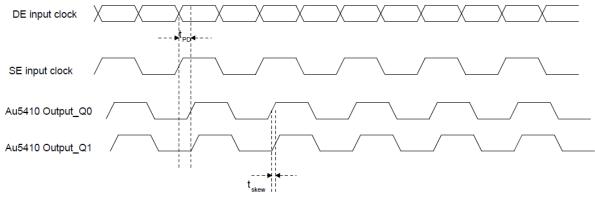

#### 4.5.2 Skew and Input to Output Delay

The parameter definitions related to propagation delay and skew are shown below.

#### 4.5.3 Rise and Fall Times

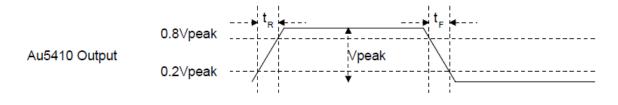

The parameter definitions related to propagation rise and fall times are shown below.

Figure 28 Parameter definitions related to rise and fall times

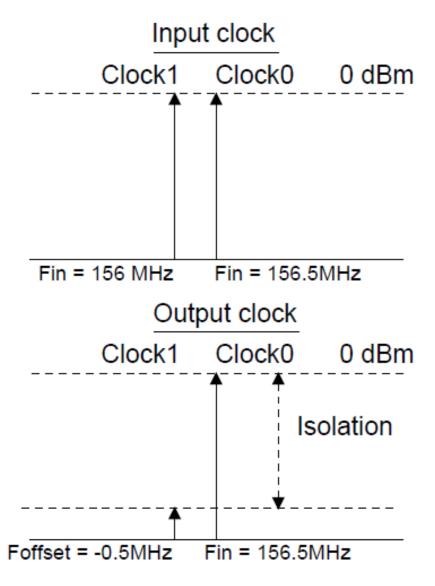

#### 4.5.4 Isolation

Isolation is a measure of the coupling of clock toggling in unselected input clock path on the output clock. Let us say that CLOCK0 path is selected and there the clock frequency is 156.5 MHz at 0 dBm power. If a clock is toggling in CLOCK1 path at 156 MHz at 0 dBm, then we there may be a tone at an offset of 0.5 MHz from the carrier, in the output clock. The power of this tone with respect to the carrier is called isolation.

Figure 29 Parameter definition of isolation

## 5 Thermal Information

#### Table 10 Thermal Metrics of Au5410

| Thermal Metric                                                     | Au5410<br>RHB<br>32 pins | Units |

|--------------------------------------------------------------------|--------------------------|-------|

| $\theta_{JA}$ Junction to ambient thermal resistance, flow = 0 m/s | 43.4                     | °C/W  |

| $\theta_{JA}$ Junction to ambient thermal resistance, flow = 1 m/s | 38.7                     | °C/W  |

| $\theta_{JA}$ Junction to ambient thermal resistance, flow = 2 m/s | 37.4                     | °C/W  |

| $\theta_{JB}$ Junction to board                                    | 16.62                    | °C/W  |

| $\theta_{JC}$ Junction to case                                     | 23.7                     | °C/W  |

| $\psi_{JT}$ Junction to top characterization parameter             | 0.75                     | °C/W  |

## 6 HOT Swap Recommendations

### 6.1 Introduction

Hot-swap is a term used to refer to the insertion and removal of a daughter card from a backplane without powering down the system power. With today's high speed data and redundancy requirements, many systems are required to run continuously without being powered down. If special considerations are not taken, the device can be damaged.

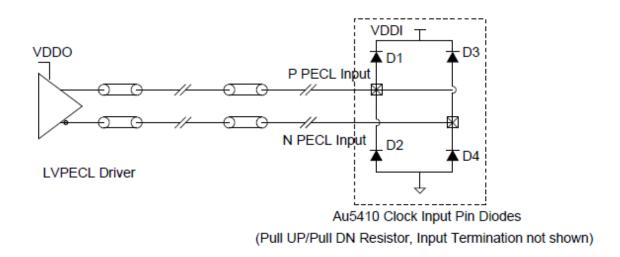

## 6.2 Typical Differential Input Clock

For example, Figure 30 shows a typical LVPECL driver and differential input. If the power of the driver (VDDO) is turned on before the input supply (VDDI), there is a possibility that the input current could exceed the limit and damage diode D1.

#### Figure 30 Typical input differential clock