## AU5248 - Low Noise PLL Based Crystal Oscillator

## **General Description**

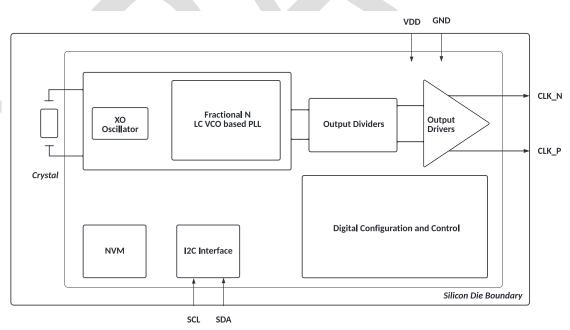

The AU5248 is a PLL based programable crystal oscillator. The device is user programmable via I2C to configure any frequency between 200 KHz to 1 GHz. AU5248 is a low Noise PLL with Integrated XTAL which provides clocks with ultra low jitter of 85 fs.

AU5248 is factory-configurable for a wide range of user selectable option including the I2C address, and output format. With on chip NVM and factory programming, Aurasemi can satisfy customer requirements with very faster lead times.

#### Applications:

- . 100G/200G/400G OTN, coherent optics

- 10G/40G/100G optical ethernet

- · 3G-SDI/12G-SDI/24G-SDI broadcast video

- Datacenter

- · Test and measurement

- · Clock and data recovery

- · FPGA/ASIC clocking

#### **Features**

- Output programmable to any frequency from 200KHz to 1GHz with 0.1ppb resolution.

Selected frequencies between 1GHz to 1.5GHz are available on special order.

- Ultra Low Jitter: 85fs Typ Jrms (12 kHz-20 MHz)

- Fractional N fully integrated PLL

- VDD supply operation at 3.3 V, 2.5 V and 1.8 V

- I2C Interface supports Standard (100 KHz) and Fast Mode(400 KHz)

- Best in class PSRR performance of -85dBC typical

- Output Driver options: LVPECL, LVDS, HCSL-LP, LVDS-Boost, HCSL,CML.

- +/- 25 ppm stability (-40 °C to 85 °C)

- Available in 3.2 mm x 2.5 mm package

**Figure 1 Functional Overview**

# **Table of Contents**

| General Description                        | 1  |

|--------------------------------------------|----|

| Features                                   |    |

| Table of Contents                          | 2  |

| List of Tables                             | 3  |

| List of Figures                            | 4  |

| 1 Pin Description                          |    |

| 2 Electrical Characteristics               |    |

| 3 Serial Programming Interface Description | 9  |

| 3.1 I2C protocol                           | 9  |

| 3.1.1 Single Byte Write                    | 10 |

| 3.1.2 Multi Byte Write                     | 10 |

| 3.1.3 Single Byte Read                     | 11 |

| 3.1.4 Multi Byte Read                      |    |

| 3.1.5 I2C Bus Timing Specifications        |    |

| 4 Package Information                      | 13 |

| 5 Output Termination Information           | 14 |

| 6 Ordering Information                     | 17 |

| 7 Pavision History                         | 19 |

## **List of Tables**

| Table 1 Pin Description               | 5  |

|---------------------------------------|----|

| Table 2 Absolute Maximum Ratings      |    |

| Table 3 Operating Temperature         |    |

| Table 4 DC Electrical Characteristics | 6  |

| Table 5 Output RMS Jitter             | 6  |

| Table 6 Clock Output Phase Noise      | 7  |

| Table 7 Power Supply Rejection        | 7  |

| Table 8 Output Clock Specifications   | 7  |

| Table 9 I2C Bus Timing Specification  | 11 |

| Table 10 Revision History             | 18 |

# **List of Figures**

| Figure 1 Functional Overview                                                         | 1  |

|--------------------------------------------------------------------------------------|----|

| Figure 2 AU5248 Top View                                                             | 5  |

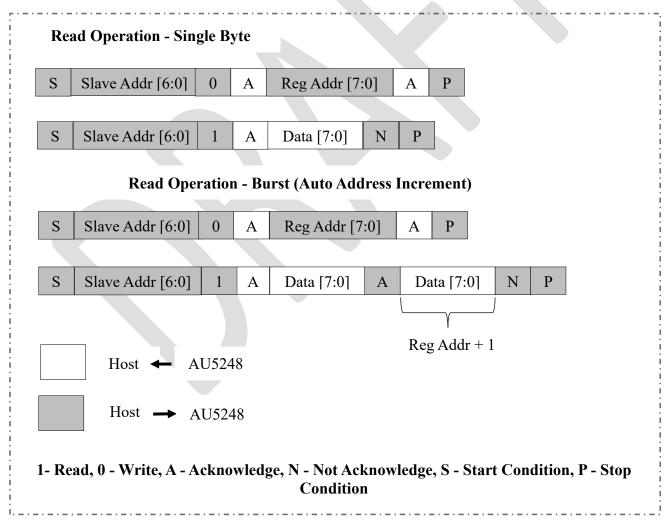

| Figure 3 I2C Read Operation                                                          |    |

| Figure 4 I2C Write Operation                                                         | 10 |

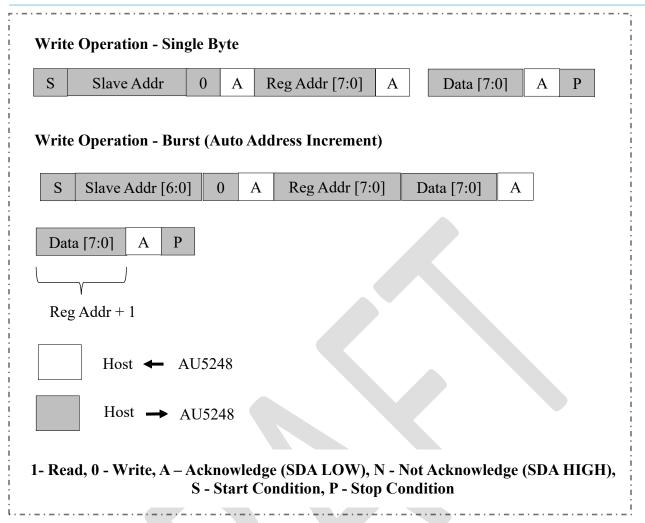

| Figure 5 I2C Timing Waveform                                                         | 12 |

| Figure 6 Package Diagram (3.2 mm x 2.5 mm)                                           | 13 |

| Figure 7 LVPECL Output Driver used with traditional DC Coupled LVPECL receiver       | 14 |

| Figure 8 LVPECL Output Driver with DC Coupled LVPECL receiver: Thevenin Equivalent   | 14 |

| Figure 9 LVDS Output Driver used with traditional DC Coupled LVDS receiver           | 14 |

| Figure 10 LVDS Output Driver used with AC Coupled terminations for various receivers | 15 |

| Figure 11 HCSL DC Coupled – Low-Power (HCSL-LP)                                      | 15 |

| Figure 12 HCSL DC Coupled - Far End Termination                                      | 16 |

| Figure 13 Output Driver with AC Coupled CML receiver                                 | 16 |

| Figure 14 Ordering Information                                                       | 17 |

# **1 Pin Description**

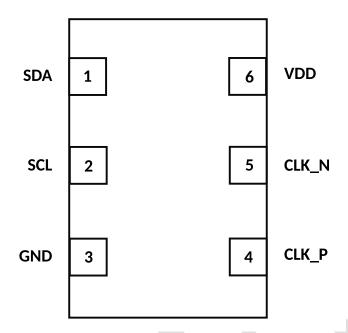

Figure 2 AU5248 Top View

**Table 1 Pin Description**

| Pin Name | Pin No. | I/O Type     | Function                         |

|----------|---------|--------------|----------------------------------|

| SDA      | 1       | Input/Output | I2C Serial Data                  |

| SCL      | 2       | Input        | I2C Serial Clock                 |

| GND      | 3       | GND          | GND                              |

| CLKP     | 4       | Output       | Clock + for differential Output. |

| CLKN     | 5       | Output       | Clock - for differential Output. |

| VDD      | 6       | Power        | Chip Power Supply                |

### **2 Electrical Characteristics**

#### **Table 2 Absolute Maximum Ratings**

| Parameter                  | Conditions                     | Symbol             | Min   | Тур | Max   | Units |

|----------------------------|--------------------------------|--------------------|-------|-----|-------|-------|

| Core Supply voltage        |                                | $V_{DD}$           | -0.5  |     | +3.63 | V     |

| Input voltage, All Inputs  | Relative to GND                | V <sub>IN</sub>    | -0.5  |     | +3.63 | V     |

| Storage temperature        | Non-functional, Non-Condensing | Ts                 | -55   |     | +150  | °C    |

| Programming Temperature    |                                | T <sub>PROG</sub>  | +15   |     | +50   | °C    |

| Programming Voltage        |                                | $V_{PROG}$         | 2.375 | 2.5 | 2.625 | V     |

| ESD (human body model)     | JEDEC JS-001-2012              | ESD <sub>HBM</sub> |       |     | 2000  | V     |

| ESD (charged device model) | JEDEC JESD22-C101E             | ESD <sub>CDM</sub> |       |     | 500   | V     |

#### Notes:

- 1. Exceeding maximum ratings may shorten the useful life of the device.

- 2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or at any other conditions beyond those indicated under the DC Electrical Characteristics is not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability or cause permanent device damage.

#### **Table 3 Operating Temperature**

| Parameter            | Conditions | Symbol | Min | Тур | Max  | Units |

|----------------------|------------|--------|-----|-----|------|-------|

| Ambient temperature  |            | TA     | -40 | _   | +105 | °C    |

| Junction temperature |            | TJ     |     |     | +125 | °C    |

#### **Table 4 DC Electrical Characteristics**

| Parameter         | Condition                     | Symbol          | Min   | Тур  | Max   | Units |

|-------------------|-------------------------------|-----------------|-------|------|-------|-------|

| Supply Voltage    | 1.8 V range: ±5%              |                 | 1.71  | 1.80 | 1.89  | V     |

|                   | 2.5 V range: ±5%              | V <sub>DD</sub> | 2.375 | 2.50 | 2.625 | V     |

|                   | 3.3 V range: ±10%             |                 | 2.97  | 3.3  | 3.63  | V     |

| Supply Current    | LVPECL                        |                 |       | 68   |       |       |

| (Output Enabled)  | LVDS                          |                 |       | 47   |       |       |

| (Output Eliabioa) | LVDS-Boost                    | IDD             |       | 51   |       | mA    |

|                   | HCSL<br>(Far End Termination) |                 |       | 59   |       |       |

|                   | HCSL-LP                       |                 |       | 50   |       |       |

| Power Up Time     |                               |                 |       | 15   |       | ms    |

#### **Table 5 Output RMS Jitter**

| Parameter                         | Conditions                    | Symbol             | Min | Тур | Max | Units  |

|-----------------------------------|-------------------------------|--------------------|-----|-----|-----|--------|

| RMS Jitter for<br>12 kHz – 20 MHz | F <sub>OUT</sub> = 622.08 MHz | DMO                |     | 0.5 |     | f      |

| Integration Bandwidth             | F <sub>OUT</sub> = 156.25 MHz | RMS <sub>JIT</sub> |     | 85  |     | fs rms |

#### Notes

1. The RMS Jitter data is based on the simulation results. Final data will be populated based on lab €characterization.

#### **Table 6 Clock Output Phase Noise**

| Offset Frequency | 156.25 MHz LVDS  | 622.08 MHz LVDS   | Units   |

|------------------|------------------|-------------------|---------|

| 1 kHz            | -120.7           | -108.7            |         |

| 10 kHz           | -132.7           | -120.7            |         |

| 100 kHz          | -143.6           | -131.6            | dBc/Hz  |

| 1 MHz            | -151.8           | -139.8            | UDC/FIZ |

| 10 MHz           | -167.9           | -159.1            |         |

| 20 MHz           | -170.6           | -162.9            |         |

| Offset Frequency | 156.25MHz LVPECL | 622.08 MHz LVPECL | Units   |

| 1 kHz            | -120.7           | -108.7            |         |

| 10 kHz           | -132.6           | -120.7            |         |

| 100 kHz          | -143.6           | -131.6            | dBc/Hz  |

| 1 MHz            | -151.7           | -139.8            | UDC/HZ  |

| 10 MHz           | -166.3           | -158.8            |         |

| 20 MHz           | -169.8           | -162.9            |         |

#### Notes:

#### **Table 7 Power Supply Rejection**

| Parameter                     | Conditions        | Symbol              | Min | Тур | Max | Units |

|-------------------------------|-------------------|---------------------|-----|-----|-----|-------|

|                               | 100 kHz Sine Wave |                     |     |     |     |       |

| F <sub>OUT</sub> = 156.25 MHz | 200 kHz Sine Wave | PSRR <sub>VDD</sub> |     | -85 |     | dBc   |

|                               | 500 kHz Sine Wave |                     |     |     |     | ubc   |

|                               | 1 MHz Sine Wave   |                     |     |     |     |       |

#### Notes

- 1. The PSRR is measured with a 50 mVpp sinusoid in series with the supply and checking the spurious level relative to the carrier on the output in terms of phase disturbance impact.

- 2. Output PSRR measured with LVDS standard which are the recommended standards for AC Coupled terminations.

- 3. The PSRR data is provided based on simulation worst case numbers. Final data will be provided based on lab characterization.

### **Table 8 Output Clock Specifications**

| Parameter                                            | Conditions                                                                   | Symbol           | Min             | Тур          | Max  | Unit |

|------------------------------------------------------|------------------------------------------------------------------------------|------------------|-----------------|--------------|------|------|

| DC Electrical Specificati                            | ons - LVDS Outputs (VDD                                                      | = 1.8 V, 2.5 V   | or 3.3 V range) | )            |      |      |

| Output Common-Mode<br>Voltage                        | VDD = 2.5 V or 3.3 V range                                                   | V <sub>OCM</sub> |                 | 1.2          |      | V    |

| Output Common-Mode<br>Voltage                        | VDD = 1.8 V                                                                  | V <sub>OCM</sub> |                 | 0.85         |      |      |

| AC Electrical Specificati                            | ons (LVPECL, LVDS, HCSL                                                      | . Far End Tern   | nination): Fout | = 156.25 MHz |      |      |

| Clock Output Frequency                               |                                                                              | f <sub>OUT</sub> | 0.2             |              | 1000 | MHz  |

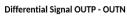

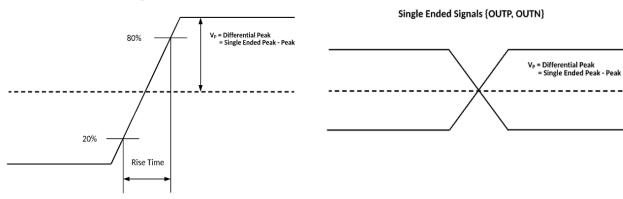

| LVPECL Output<br>Rise/Fall Time                      | 20% to 80% of AC<br>levels. Measured at<br>156.25 MHz for LVPECL<br>outputs. | t <sub>RF</sub>  |                 |              | 350  | ps   |

| LVDS Output Rise/Fall<br>Time                        | 20% to 80% of AC<br>levels. Measured at<br>156.25 MHz for LVDS<br>outputs.   | t <sub>RF</sub>  |                 |              | 350  | ps   |

| LVDS-Boost Output<br>Rise/Fall Time                  | 20% to 80% of AC<br>levels. Measured at<br>156.25 MHz for LVDS<br>outputs.   | t <sub>RF</sub>  |                 |              | 350  | ps   |

| HCSL Far End<br>Termination Output<br>Rise/Fall Time | 20% to 80% of AC<br>levels. Measured at<br>156.25 MHz for HCSL<br>outputs.   | t <sub>RF</sub>  |                 |              | 350  | ps   |

| Output Duty Cycle                                    | Measured at differential 50% level, 156,25 MHz                               | t <sub>ODC</sub> | 45              | 50           | 55   | %    |

<sup>1.</sup> The Clock Output Phase Noise data is based on the simulation. Final Phase Noise data will be populated based on lab Characterization.

| Parameter                                               | Conditions                                   | Symbol                 | Min | Тур    | Max | Unit |

|---------------------------------------------------------|----------------------------------------------|------------------------|-----|--------|-----|------|

| LVPECL Output<br>Differential peak                      | Measured at 156.25M<br>Output                | VP                     |     | 750    |     |      |

| LVDS Output differential peak                           | Measured at 156.25M<br>Output                | VP                     |     | 400    |     |      |

| LVDS-Boost Output differential peak                     | Measured at 156.25M<br>Output                | VP                     |     | 790    |     | mV   |

| HCSL Far End<br>Termination Output<br>differential peak | Measured at 156.25M<br>Output                | VP                     |     | 800    |     |      |

| AC Electrical Specificati                               | ons (HCSL – LP)                              |                        |     |        |     |      |

| Slew Rate                                               | Scope Averaging on                           | dV/dt                  | 1   |        | 4   | V/ns |

| Slew Rate Matching                                      | Single-ended measurement.                    | ΔdV/dt                 |     |        | 20  | %    |

| Maximum Voltage                                         | Measurement on single ended signal           | V <sub>MAX</sub>       |     | 850    |     | mV   |

| Minimum Voltage                                         | using absolute value. (Scope averaging off). | V <sub>MIN</sub>       |     | 0      |     | mV   |

| Crossing Voltage (abs)                                  | Scope averaging off.                         | V <sub>cross_abs</sub> |     | 430    |     | mV   |

| Crossing Voltage (var)                                  | Scope averaging off.                         | Δ-V <sub>cross</sub>   |     | 9.6    |     | mV   |

| Differential Impedance                                  |                                              | Z <sub>DIFF</sub>      |     | 85/100 |     | Ω    |

Notes:

Convention for Wave Forms

## 3 Serial Programming Interface Description

The chip settings can be reconfigured using the I2C serial programming interface.

#### 3.1 I2C protocol

Pin configuration of serial interface in I2C slave mode is as follows.

- SCL

- SDA

The device uses the SDA and SCL pins for a 2-wire serial interface that operates up to 400 Kb/s in Read and Write modes. It complies with the I2C bus standard. The I2C access protocol in device is both random and sequential access for Write and Read modes.

The I2C serial interface can operate at either Standard rate (100 Kbps) or Fast rate (400 Kbps).

The default I2C address will be 0x55, The Device will support to configure any I2C address through One Time Programming.

Figure 3 I2C Read Operation

Figure 4 I2C Write Operation

#### 3.1.1 Single Byte Write

- The master initiates the transaction by issuing a start condition, writes 7-bit slave address and then the read/write bit is written as 0 (write)

- The slave acknowledges by driving zero on the bus

- The master then writes the 8-bit register map address

- The slave acknowledges by driving zero on the bus

- The master then writes the 8-bit data to be written to the register map address specified

- The slave acknowledges by driving zero on the bus

- The master ends the transaction by issuing a stop condition

#### 3.1.2 Multi Byte Write

- The master initiates the transaction by issuing a start condition, writes 7-bit slave address and then the read/write bit is written as 0 (write)

- o The slave acknowledges by driving zero on the bus

- The master then writes the 8-bit register map address

- The slave acknowledges by driving zero on the bus

- The master then writes the 8-bit data to be written to the register map address specified

- The slave acknowledges by driving zero on the bus and increment the address by 1

- The master continuously writes the 8-bit data to the slave and the slave will acknowledge by driving zero for every byte.

- The master ends the transaction by issuing a stop condition

#### 3.1.3 Single Byte Read

- The master initiates the transaction by issuing a start condition, writes 7-bit slave address and then the read/write bit is written as 0 (write)

- The slave acknowledges by driving zero on the bus

- The master then writes the 8-bit register map address

- o The slave acknowledges by driving zero on the bus

- The master ends the transaction by issuing a stop condition

- The master re-initiates the transaction by issuing a start condition, writes 7-bit slave address and then the read/write bit is written as 1 (read)

- o The slave then writes the 8-bit data to be written to the register map address specified

- The master does not acknowledge this transaction as the slave may assume a multi-byte read operation and there is a risk of slave holding the bus low

- The master ends the transaction by issuing a stop condition

#### 3.1.4 Multi Byte Read

The multi-byte read mode is used to read a continuous segment of the register map. The multi-byte read is faster than performing multiple single byte reads as the device address and register map address need not be specified for every byte read from the register map

- The master initiates the transaction by issuing a start condition, writes 7-bit slave address and then the read/write bit is written as 0 (write)

- The slave acknowledges by driving zero on the bus

- The master then writes the 8-bit register map address

- The slave acknowledges by driving zero on the bus

- The master ends the transaction by issuing a stop condition

- The master re-initiates the transaction by issuing a start condition, writes 7-bit slave address and then the read/write bit is written as 1 (read)

- o The slave then writes the 8-bit data to be written to the register map address specified

- The master acknowledges by driving zero on the bus

- The slave automatically increments the register map address and writes the data in at that address to the bus and the master acknowledges

- o When all bytes of data are read, master ends the operation by not acknowledging the last read

- The master then ends the transaction by issuing a stop condition.

### 3.1.5 I2C Bus Timing Specifications

**Table 9 I2C Bus Timing Specification**

| Description                                     | Symbol              | Standard Mode |          | Fast Mode |     | Units  |

|-------------------------------------------------|---------------------|---------------|----------|-----------|-----|--------|

|                                                 |                     | Min           | Max      | Min       | Max | Ullits |

| SCL clock frequency                             | fscL                | _             | 100      | _         | 400 | kHz    |

| Hold time START condition                       | thd:STA             | 0.4           | _        | 0.6       | _   | μs     |

| Low period of the SCK clock                     | tLOW                | 4.7           | _        | 1.3       | _   | μs     |

| High period of the SCK clock                    | tнібн               | 4.0           | _        | 0.6       | _   | μs     |

| Setup time for a repeated START                 | touera              | 4.7           |          | 0.6       | _   | He     |

| condition                                       | t <sub>SU:STA</sub> | 4.7           |          | 0.0       | _   | μs     |

| Data hold time                                  | t <sub>HD:DAT</sub> | 300           | _        | 300       | _   | ns     |

| Data setup time                                 | t <sub>SU:DAT</sub> | 100           | _        | _         | _   | ns     |

| Rise time                                       | t <sub>R</sub>      | _             | 1000     | _         | 300 | ns     |

| Fall time                                       | tF                  | _             | 300      | _         | 300 | ns     |

| Setup time for STOP condition                   | tsu:sto             | 4.0           | _        | 0.6       | _   | μs     |

| Bus-free time between STOP and START conditions | t <sub>BUF</sub>    | 4.7           | _        | 1.3       | _   | μs     |

| C 17 II C 1 CONTAILLOND                         |                     |               | <u> </u> | <u> </u>  |     |        |

| Description                 | Symbol              | Standard Mode |      | Fast Mode |     | Units  |

|-----------------------------|---------------------|---------------|------|-----------|-----|--------|

| Description                 |                     | Min           | Max  | Min       | Max | Ullits |

| Data valid time             | t <sub>VD;DAT</sub> | _             | 3.45 | _         | 0.9 | μs     |

| Data valid acknowledge time | tvd;ack             | _             | 0.9  | _         | 0.9 | μs     |

#### Note:

• In I2C mode, the serial data and clock have an on-chip 25 k $\Omega$  pull up resistor to VDDIO. Please refer Figure 5 for the nomenclature of these parameters.

Figure 5 I2C Timing Waveform

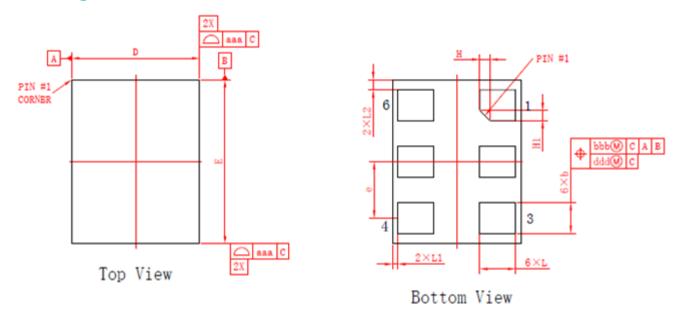

# **4 Package Information**

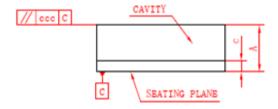

Side View

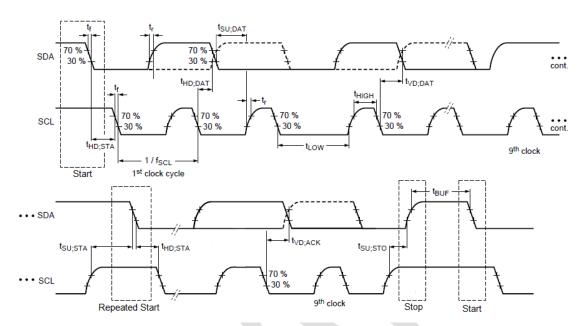

Figure 6 Package Diagram (3.2 mm x 2.5 mm)

| Symbol | Millimeter |       |       |  |  |

|--------|------------|-------|-------|--|--|

|        | MIN        | NOM   | MAX   |  |  |

| A      | 0.810      | 0.910 | 1.010 |  |  |

| С      | 0.170      | 0.210 | 0.250 |  |  |

| D      | 2.450      | 2.500 | 2.550 |  |  |

| E      | 3.150      | 3.200 | 3.250 |  |  |

| Н      | -          | 0.200 | -     |  |  |

| H1     | -          | 0.200 | -     |  |  |

| L      | 0.625      | 0.700 | 0.775 |  |  |

| L1     | 0.025      | 0.100 | 0.175 |  |  |

| L2     | 0.125      | 0.200 | 0.275 |  |  |

| е      | -          | 1.100 | -     |  |  |

| b      | 0.550      | 0.600 | 0.650 |  |  |

| aaa    |            | 0.150 |       |  |  |

| bbb    |            | 0.150 |       |  |  |

| CCC    |            | 0.100 |       |  |  |

| ddd    |            | 0.080 |       |  |  |

# **5 Output Termination Information**

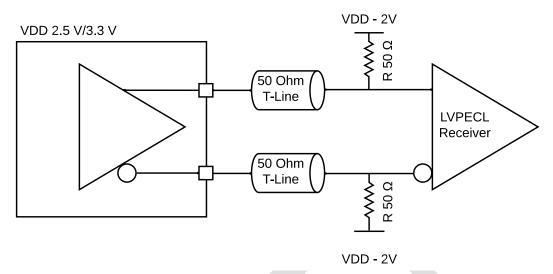

Figure 7 LVPECL Output Driver used with traditional DC Coupled LVPECL receiver

2.5 V

250 Ω

62.5 Ω

3.3 V

127 Ω

82.5 Ω

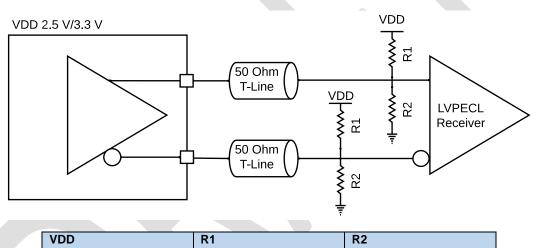

Figure 8 LVPECL Output Driver with DC Coupled LVPECL receiver: Thevenin Equivalent

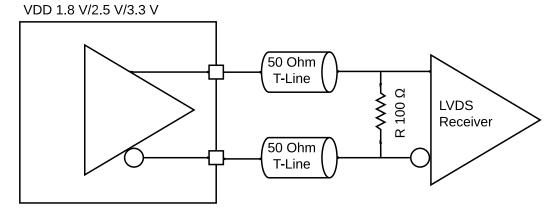

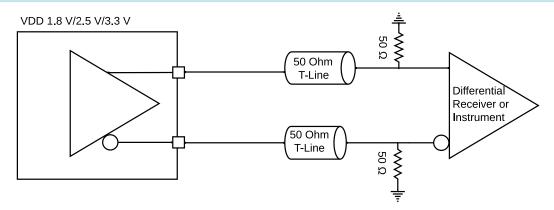

Figure 9 LVDS Output Driver used with traditional DC Coupled LVDS receiver

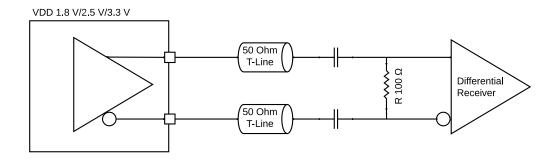

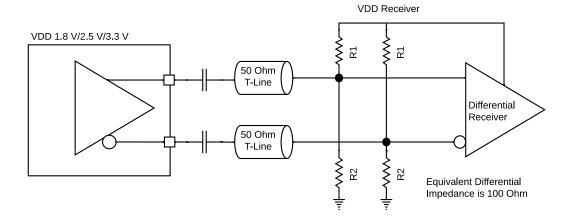

Figure 10 LVDS Output Driver used with AC Coupled terminations for various receivers

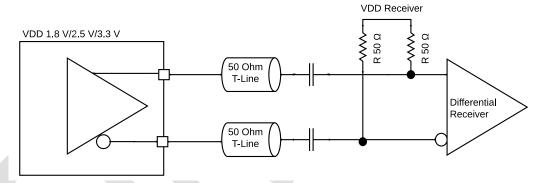

Figure 11 HCSL-LP (Low Power) DC Coupled

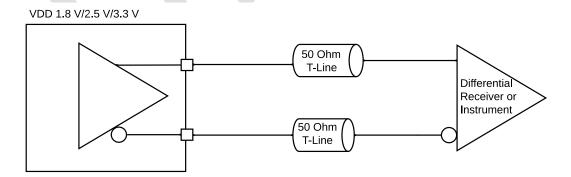

Figure 12 HCSL DC Coupled - Far End Termination

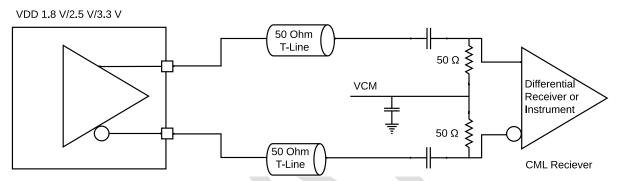

Figure 13 Output Driver with AC Coupled CML receiver

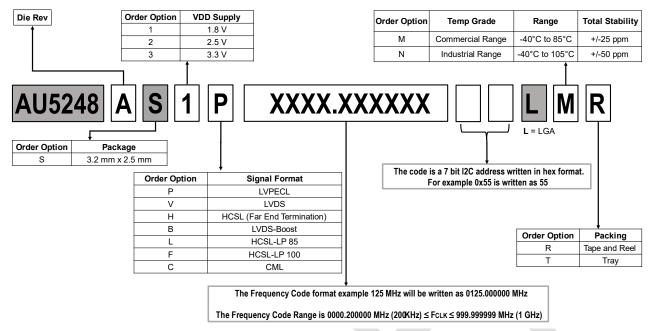

## **6 Ordering Information**

**Figure 14 Ordering Information**

# **7 Revision History**

## **Table 10 Revision History**

| Version | Date                      | Description                                   | Author   |

|---------|---------------------------|-----------------------------------------------|----------|

| 0.1     | 11 <sup>th</sup> Jan 2023 | AU5248 Advanced Datasheet First Draft Created | Aurasemi |

#### **IMPORTANT NOTICE AND DISCLAIMER**

AURASEMI PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Aurasemi products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Aurasemi grants you permission to use these resources only for development of an application that uses Aurasemi products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Aurasemi intellectual property or to any third-party intellectual property. Aurasemi disclaims responsibility for, and you will fully indemnify Aurasemi and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Aurasemi products are provided only subject to Aurasemi Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Aurasemi resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

### **Contact Information**

For more information visit www.aurasemi.com

For sales related information please send an email to sales@aurasemi.com

#### **Trademarks**

Aurasemi and Aurasemi Logo are trademarks of Ningbo Aura Semiconductor Private Limited. All referenced brands, product names, service names and trademarks are the property of their respective owners.