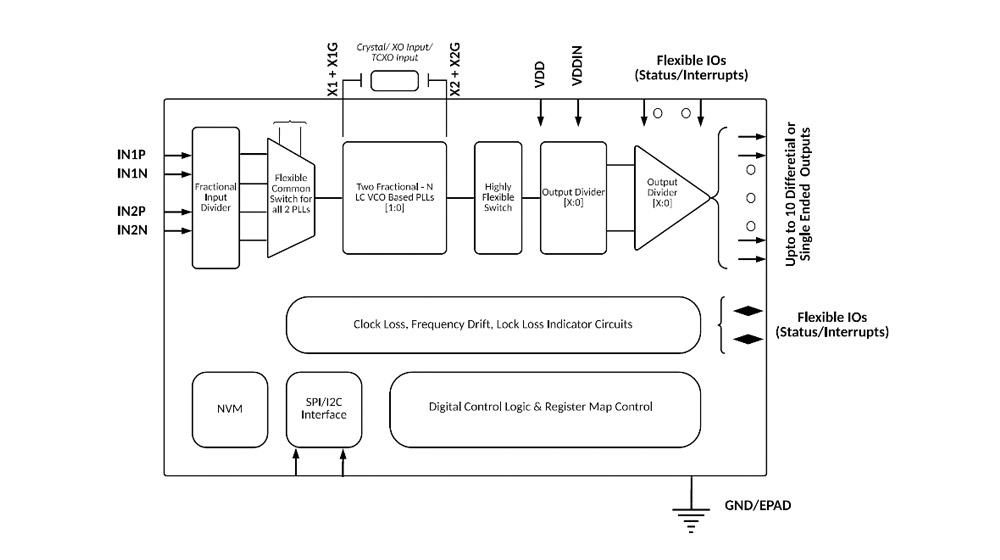

• 从 4 个输入中的 1 个进行双 PLL 频率转换

• DPLL 可编程带宽 1mHz - 4KHz

• 数控振荡器模式,频率步进分辨率高达0.005ppb

• 输入时钟无中断切换,支持自动或手动模式,切换时钟产生的最大相位差仅50ps

• 支持外部反馈连接的 ZDM

• OTN/PTN

• BBU/RRU

• 支持 SyncE 的 LAN 交换机/路由器

• 小型蜂窝

• 加速卡

• 较低的相位噪声可最大限度地降低系统中的误码率

• 更好的信号完整性可提高设计裕量并缩短上市时间

• 更高的时钟树集成度可减少系统 BOM 并提高整体可靠性