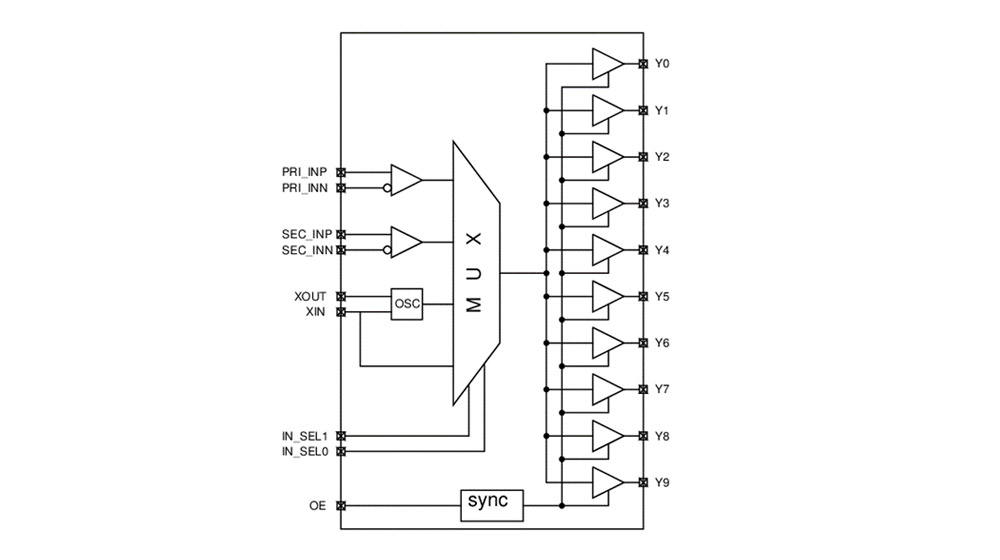

• 输入可以是LVPECL,LVDS,LVCMOS,SSTL,HCSL和XTAL波形。

• 支持 8 MHz 至 50 MHz 的晶振频率

• 用于输出同步的输出使能 (OE) 信号

• 输出各时钟信号之间相对偏移时间典型值为30ps

• 内核电源电压为 3.3 V/2.5 V/1.8 V 和 LVCMOS 输出电源电压为 3.3 V/2.5 V/1.8 V/1.5 V 的电平转换

• 无线通信

• 网络和数据通信

• 医疗设备

• 自动化和测试设备

• 高端音频/视频

• 低附加抖动和低输出至输出偏斜,非常适合抖动/相位敏感型应用

• 宽工作电压,确保设计兼容性

• 低功耗,是便携式和高密度应用的理想选择