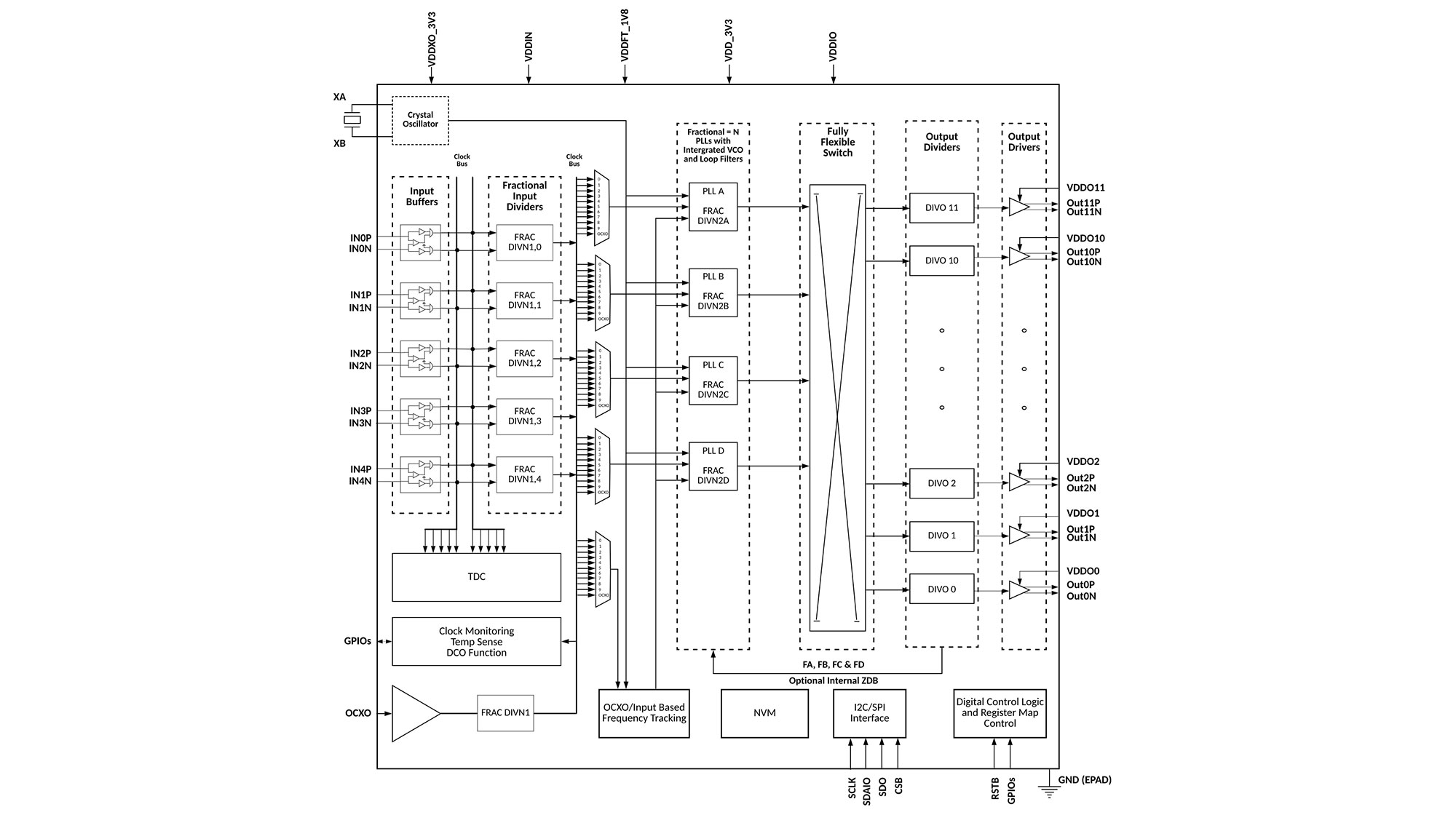

• 来自 4 个输入中的任何一个的四通道 PLL 频率转换

• IEEE1588/SyncE/1 PPS 支持 1 PPS 输入锁定时间 <20s

• 一流的数控振荡器 (DCO) 模式和无中断切换

• 所有输入时钟均提供时间数字转换器 (TDC) 模式,以 10 ps <精度测量输入延迟:提供 10 个 TDC 通道(独立于 PLL)

• 具有<0.5 ns输入至输出延迟变化的内部ZDB模式

• 支持JESD204B/C 协议

• OTN/PTN

• BBU/RRU

• 100/200/400G/800G 支持同步的交换机/路由器

• 小型蜂窝

• 加速卡

• 较低的相位噪声可最大限度地降低系统中的误码率

• 更好的信号完整性可提高设计余量并缩短上市时间

• 更高的时钟树集成度可减少系统 BOM 并提高整体可靠性